132

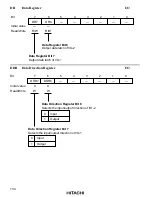

TCSR Timer Control/Status Register

WDT

7

UDF

0

R/W

6

EWE

0

R/(W)*

5

—

1

R

4

HLT

0

R/W

3

—

1

R

0

CS0

0

R/W

2

—

1

R

1

CS1

0

R/W

Bit

Initial value

Read/Write

Clock Select 1 and 0

0

1

0

1

0

1

CLK/32

CLK/64

CLK/128

CLK/256

Halt Flag

0

1

Normal operation

On-chip functions stop

ECR Write Enable

0

1

[Clearing condition]

When EEPMOV instruction execution ends

[Setting conditon]

When 1 is written to this bit while it is 0

Underflow Flag

0

1

[Clearing condition]

When RTE instruction is executed while UDF = 1

[Setting conditon]

When TCNT underflow occurs (H'00

→

H'FF)

Note: Only 1 can be written to bit 6 to set the flag.

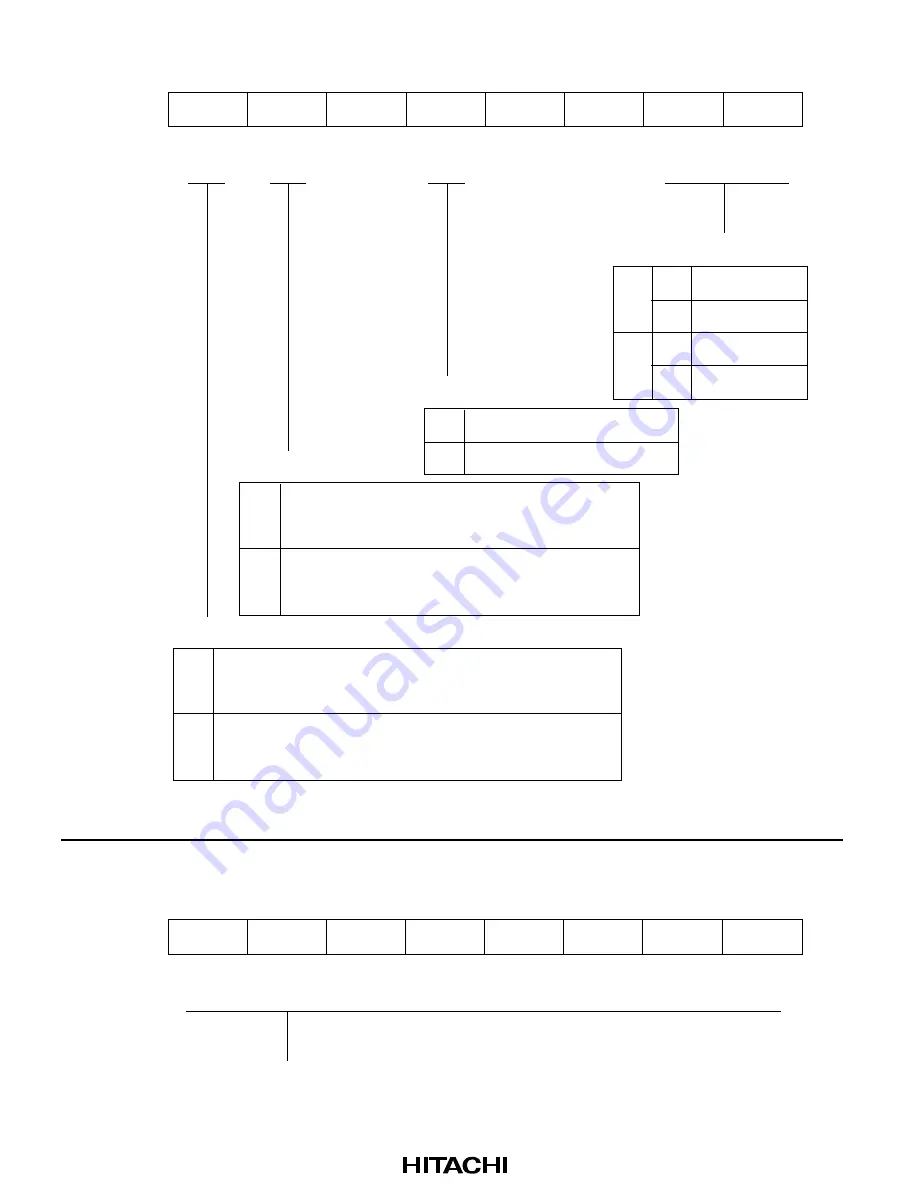

TCNT Timer Counter

WDT

Bit

Initial value

Read/Write

Timer count

7

1

R/W

6

1

R/W

5

1

R/W

4

1

R/W

3

1

R/W

0

1

R/W

2

1

R/W

1

1

R/W