59

5.1.4

Vector Configuration

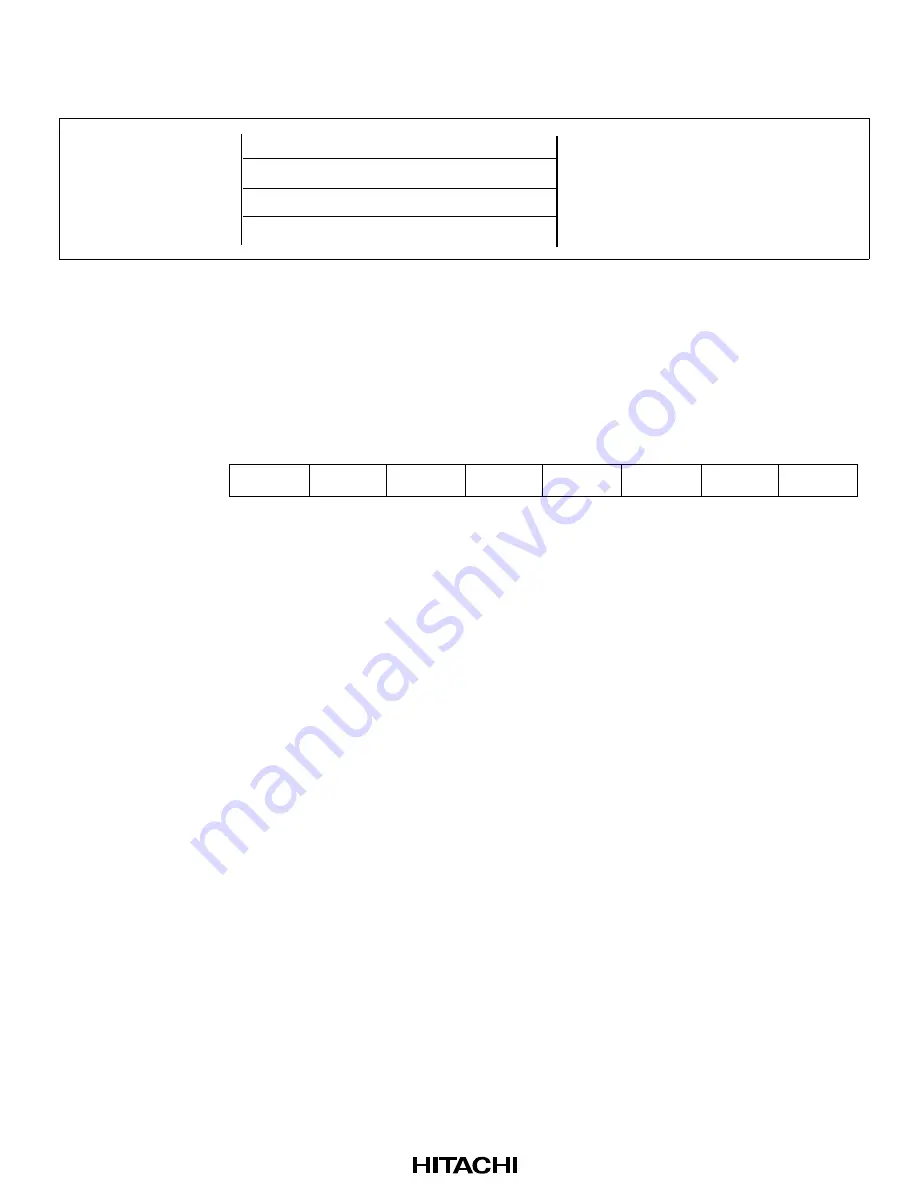

Figure 5.2 shows the memory map of the WDT vector area.

EWE interrupt vector

UDF interrupt vector

Address

H'000A/H'000B

H'000C/H'000D

Figure 5.2 WDT Vectors

5.2

Register Descriptions

5.2.1

Timer Counter (TCNT)

Bit:

7

6

5

4

3

2

1

0

Initial value:

1

1

1

1

1

1

1

1

Read/Write:

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

TCNT is an 8-bit readable and writable down-counter. Before TCSR is written to after reset,

TCNT decrements the value by counting internal clocks for the CPU regardless of the CS1 and

CS0 bit settings in TCSR. Therefore, if the WDT is not initialized within 512 external clock cycles

from the rising edge of the

RES

signal when the CPUCS0 bit of SYSCR is 0 or within 256

external clock cycles from the rising edge of the

RES

signal when the CPUCS0 bit of SYSCR is 1,

a TCNT underflow (H'00

→

H'FF) occurs. When TCSR is written to after reset, TCNT starts

decrementing the value by counting pulses of the internal clock selected by the CS1 and CS0 bits

in TCSR. The number of clock cycles before TCNT underflows depends on the CS1 and CS0 bit

settings. When a TCNT underflow occurs, the UDF bit in TCSR is set to 1, then a UDF interrupt

is issued; TCNT starts decrementing from the initially written value.

TCNT is initialized to H'FF at reset or when the CS1 and CS0 bits in TCSR are written to. TCNT

can be written to only once after TCSR is written to after reset. TCNT decrementation starts from

the written value.

When the WAD bit in TCWA is 1, if once written, TCNT cannot be written to again until the chip

is reset by a low-level input to the

RES

pin.

When the WAD bit is 0, the initially written data can be reloaded to TCNT at any time even if it

has already been once written. To reload the initially written data, place an instruction for writing