197

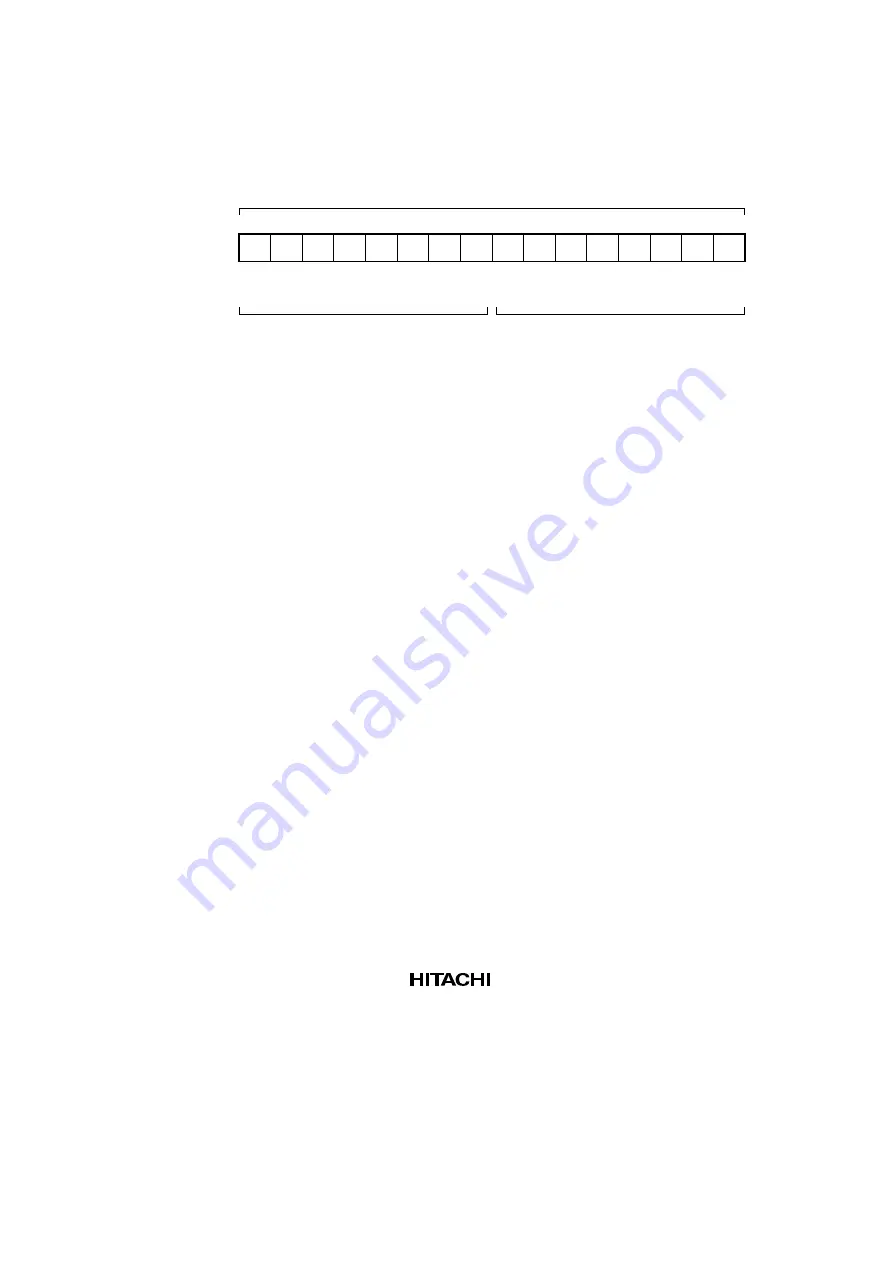

2. 16-bit output compare register (OCRF)

8-bit output compare register (OCRFH)

8-bit output compare register (OCRFL)

15

14

13

12

11

10

9

8

OCRF

OCRFH

OCRFL

7

6

5

4

3

2

1

0

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W

Bit:

Initial value:

Read/Write:

OCRF is a 16-bit read/write register composed of the two registers OCRFH and OCRFL. In

addition to the use of OCRF as a 16-bit register with OCRFH as the upper 8 bits and OCRFL as

the lower 8 bits, OCRFH and OCRFL can also be used as independent 8-bit registers.

OCRFH and OCRFL can be read and written by the CPU, but when they are used in 16-bit mode,

data transfer to and from the CPU is performed via a temporary register (TEMP). For details of

TEMP, see 9.4.3, CPU Interface.

OCRFH and OCRFL are each initialized to H'FF upon reset.

a. 16-bit mode (OCRF)

When CKSH2 is cleared to 0 in TCRF, OCRF operates as a 16-bit register. OCRF contents are

constantly compared with TCF, and when both values match, CMFH is set to 1 in TCSRF. At

the same time, IRRTFH is set to 1 in IRR2. If IENTFH in IENR2 is 1 at this time, an interrupt

request is sent to the CPU.

Toggle output can be provided from the TMOFH pin by means of compare matches, and the

output level can be set (high or low) by means of TOLH in TCRF.

b. 8-bit mode (OCRFH/OCRFL)

When CKSH2 is set to 1 in TCRF, OCRFH and OCRFL operate as two independent 8-bit

registers. OCRFH contents are compared with TCFH, and OCRFL contents are with TCFL.

When the OCRFH (OCRFL) and TCFH (TCFL) values match, CMFH (CMFL) is set to 1 in

TCSRF. At the same time, IRRTFH (IRRTFL) is set to 1 in IRR2. If IENTFH (IENTFL) in

IENR2 is 1 at this time, an interrupt request is sent to the CPU.

Toggle output can be provided from the TMOFH pin (TMOFL pin) by means of compare

matches, and the output level can be set (high or low) by means of TOLH (TOLL) in TCRF.