81

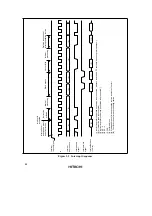

PC and CCR

saved to stack

SP (R7)

SP – 1

SP – 2

SP – 3

SP – 4

Stack area

SP + 4

SP + 3

SP + 2

SP + 1

SP (R7)

Even address

Prior to start of interrupt

exception handling

After completion of interrupt

exception handling

Notation:

PC

H

:

PC

L

:

CCR:

SP:

Upper 8 bits of program counter (PC)

Lower 8 bits of program counter (PC)

Condition code register

Stack pointer

Notes:

CCR

CCR

PC

H

PC

L

1.

2.

*

PC shows the address of the first instruction to be executed upon

return from the interrupt handling routine.

Register contents must always be saved and restored by word access,

starting from an even-numbered address.

Ignored on return.

*

Figure 3.4 Stack State after Completion of Interrupt Exception Handling

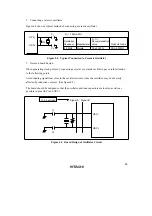

Figure 3.5 shows a typical interrupt sequence.