Rev. 3.0, 03/01, page 200 of 390

14.2.16

HSET Data Register (HSET)

HSET, a 32-bit Read/Write register, is a channel via which the system can write HSET DAC data

to CODEC or read HSET ADC data from CODEC. Bits 31-20 are reserved. The other bits are

initialized to 0 at reset. HSET is not initialized in STANDBY mode.

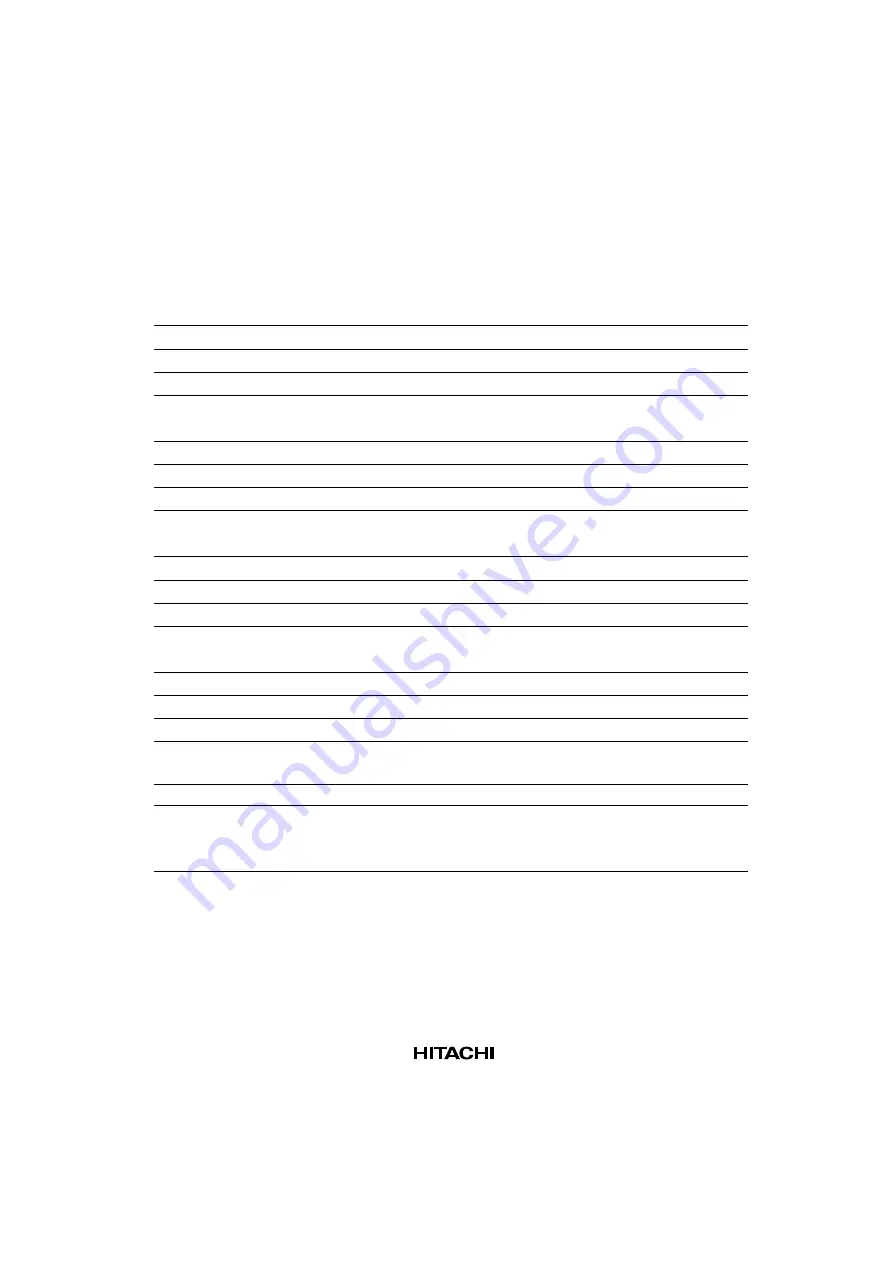

Bit

31

30

29

28

27

26

25

24

Bit Name

-

-

-

-

-

-

-

-

Initial Value

-

-

-

-

-

-

-

-

R/W

-

-

-

-

-

-

-

-

Bit

23

22

21

20

19

18

17

16

Bit Name

-

-

-

-

D19

D18

D17

D16

Initial Value

-

-

-

-

0

0

0

0

R/W

-

-

-

-

R/W

R/W

R/W

R/W

Bit

15

14

13

12

11

10

9

8

Bit Name

D15

D14

D13

D12

D11

D10

D9

D8

Initial Value

0

0

0

0

0

0

0

0

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

Bit

7

6

5

4

3

2

1

0

Bit Name

D7

D6

D5

D4

D3

D2

D1

D0

Initial Value

0

0

0

0

0

0

0

0

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

Bit

Description

Default

31 - 20

Reserved

-

19 - 0

Data 19-0 (D19-0): When this register is written, these bits will be written to the first empty

entry of HSET TX FIFO and then be transmitted to the connected CODEC.

When this register is read, the first non-empty entry of HSET RX FIFO will be read. HSET

RX FIFO stores HSET ADC data from the connected CODEC.

0

Summary of Contents for HD64465

Page 25: ...Rev 3 0 03 01 page 6 of 390 ...

Page 59: ...Rev 3 0 03 01 page 40 of 390 ...

Page 97: ...Rev 3 0 03 01 page 78 of 390 ...

Page 147: ...Rev 3 0 03 01 page 128 of 390 ...

Page 199: ...Rev 3 0 03 01 page 180 of 390 ...

Page 247: ...Rev 3 0 03 01 page 228 of 390 ...

Page 385: ...Rev 3 0 03 01 page 366 of 390 ...

Page 389: ...Rev 3 0 03 01 page 370 of 390 ...

Page 409: ...Rev 3 0 03 01 page 390 of 390 ...