Rev. 3.0, 03/01, page 241 of 390

15.6

Interrupt

An AFE interface is capable of generating five interrupts. Among these interrupts, four interrupts

of TDEI, RDFI, TERI, and RERI are issued by setting the enable bits in CTR to 1. On the other

hand, an interrupt of RDWT is masked by setting the RDETM bit to 1.

Interrupt

Source

Issuance Condition

How to clear the interrupt

TDEI

Transmit register or buffer includes no transmit data.

Clear the TDE bit in STR

RDFI

Receive register or buffer is full of received data.

Clear the RDF bit in STR

TERI

Next data transmit starts while no transmit data is

included.

Clear the TERR bit in STR

RERI

Receive register or buffer receives the next data in

spite of being in the full status.

Clear the RERR bit in STR

RDET

When a low level is input to the RING pin (this is a

level interrupt).

Write 1 to the RSW bit in CTR

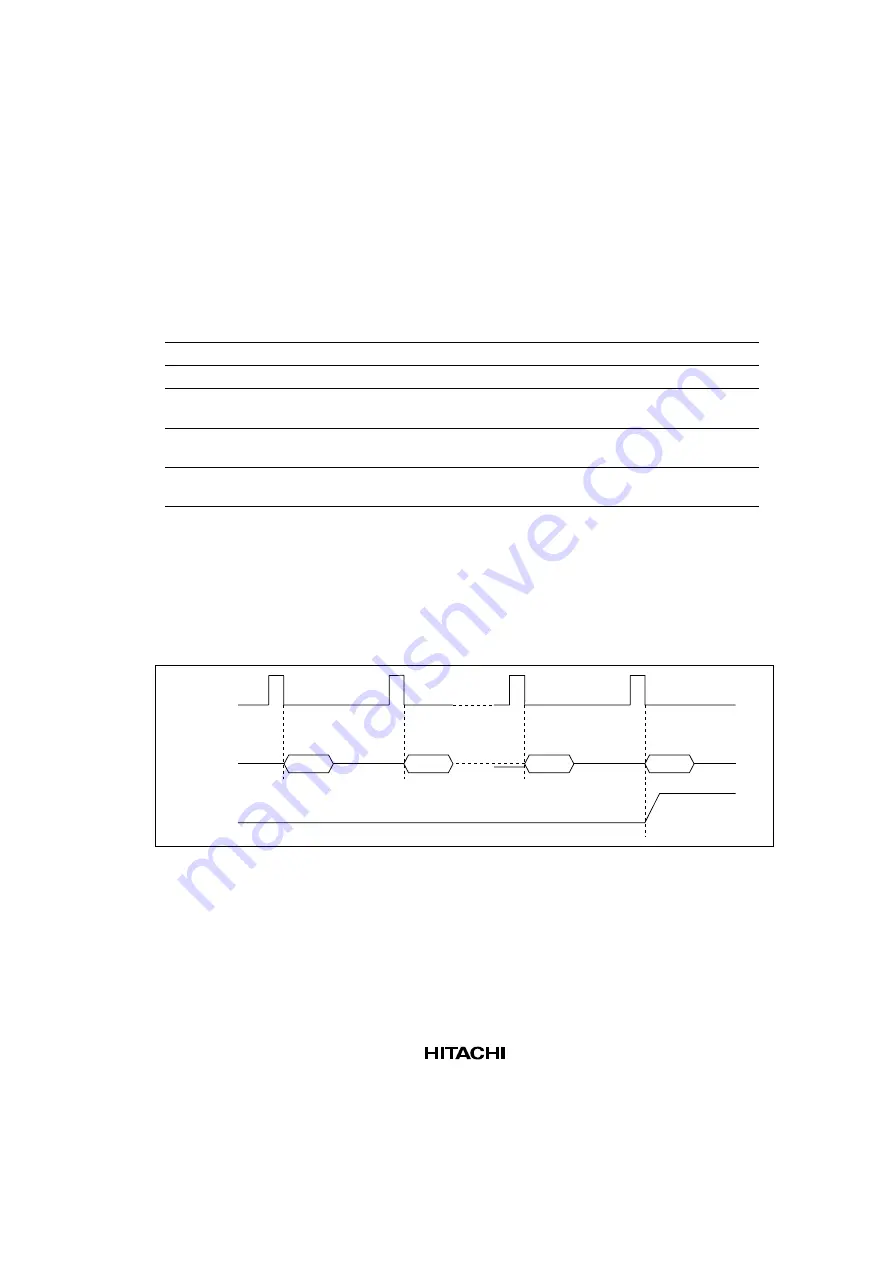

Figures 15-4 and 15-5 shown below display the output timings of TDEI and RDFI.

For timings of TERI and RERI, TERI is output when the last word data transmission starts while

RERI is output when the last word data transmission is completed. When the BUFD bit is set to 1,

transmission is performed in 1 word, but output timings do not differ from those of TDEI and

RDFI.

FS

DIN

(TxD)

data48

data47

data2

data1

TDEI

Figure 15.4 TDEI Output Timing

Summary of Contents for HD64465

Page 25: ...Rev 3 0 03 01 page 6 of 390 ...

Page 59: ...Rev 3 0 03 01 page 40 of 390 ...

Page 97: ...Rev 3 0 03 01 page 78 of 390 ...

Page 147: ...Rev 3 0 03 01 page 128 of 390 ...

Page 199: ...Rev 3 0 03 01 page 180 of 390 ...

Page 247: ...Rev 3 0 03 01 page 228 of 390 ...

Page 385: ...Rev 3 0 03 01 page 366 of 390 ...

Page 389: ...Rev 3 0 03 01 page 370 of 390 ...

Page 409: ...Rev 3 0 03 01 page 390 of 390 ...