Rev. 3.0, 03/01, page 351 of 390

Table 20.8

Parallel Port AC Timing Spec. (unit : ns)

Symbol

Parameter

Min.

Max

Comment

t

PPIRQD1

Delay from ACK# asserted to IRQ0# asserted

-

100

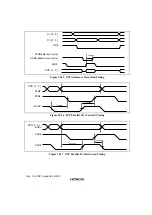

Figure 20.13

t

PPIRQD2

Delay from ACK# deasserted to IRQ0# deasserted

-

100

Figure 20.13

t

PPSLIND1

SLIN# deassert to BUSY asserted (EPP write

address cycle)

65

460

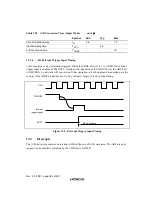

Figure 20.14

t

PPSLIND1

AFD# deassert to BUSY asserted (EPP write data

cycle)

65

460

Figure 20.14

t

PPSLIND2

SLIN # deassert to BUSY asserted (EPP read data

cycle)

65

460

Figure 20.15

t

PPSLIND2

AFD# deassert to BUSY asserted (EPP read data

cycle)

65

460

Figure 20.15

t

PPSTBD1

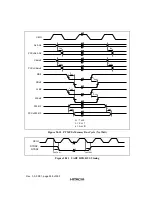

STB# asserted to BUSY deasserted (forward)

-

750

Figure 20.16

t

PPSTBD2

STB# deasserted to BUSY asserted (forward)

-

900

Figure 20.16

t

PPAFDD1

AFD# asserted to BUSY asserted (backward)

-

1100

Figure 20.17

t

PPAFDD2

AFD# deasserted to ACK# deasserted (backward)

-

800

Figure 20.17

Table 20.9

SCDI AC Timing Spec. (unit : ns)

Symbol

Parameter

Min.

Max

Comment

t

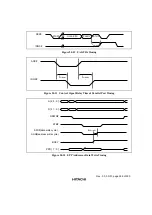

RST_LOW

ACRST# Active Low Pulse Width

1000

-

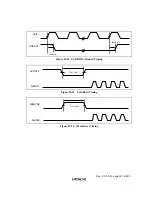

Figure 20.19

t

SYN_HIGH

SIBSYNC Active HIGH Pulse Width

1000

-

Figure 20.20

t

SYNCD1

SIBSYNC Delay Time 1

-

15

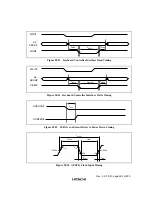

Figure 20.21

t

SYNCD2

SIBSYNC Delay Time 2

-

15

Figure 20.21

t

SDOUTD

SIBDOUT Delay Time

-

15

Figure 20.21

t

DREQ1D1

DREQ1# Delay Time 1

-

15

Figure 20.18

t

DREQ1D2

DREQ1# Delay Time 2

-

15

Figure 20.18

t

SDINSU

SIBDIN Setup Time

10

-

Figure 20.21

t

SDINHD

SIBDIN Hold Time

10

-

Figure 20.21

Summary of Contents for HD64465

Page 25: ...Rev 3 0 03 01 page 6 of 390 ...

Page 59: ...Rev 3 0 03 01 page 40 of 390 ...

Page 97: ...Rev 3 0 03 01 page 78 of 390 ...

Page 147: ...Rev 3 0 03 01 page 128 of 390 ...

Page 199: ...Rev 3 0 03 01 page 180 of 390 ...

Page 247: ...Rev 3 0 03 01 page 228 of 390 ...

Page 385: ...Rev 3 0 03 01 page 366 of 390 ...

Page 389: ...Rev 3 0 03 01 page 370 of 390 ...

Page 409: ...Rev 3 0 03 01 page 390 of 390 ...