Rev. 3.0, 03/01, page 358 of 390

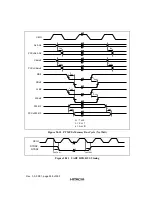

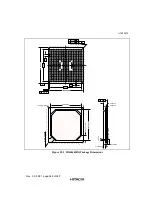

CKIO

A25-A0

PCCnA25-A0

t

AD

t

AD

CEmx#

PCCnCEmx#

t

CSD

t

CSD

RD#

RDx#

WE#

WEx#

D15-D0

PCCnD15-D0

n = 0 or 1

x = A or B

t

RSD

t

RSD

t

WED

t

WED

t

WDD

t

WDD

m : 1 or 2

Figure 20.10 PCMCIA Memory Bus Cycle (No Wait)

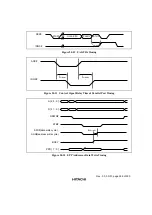

CKIO

t

URDTRD1

t

URDTRD2

DTR0#,

RTS0#

Figure 20.11 UART DTR, RTS Timing

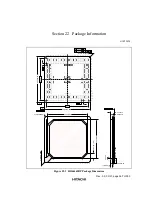

Summary of Contents for HD64465

Page 25: ...Rev 3 0 03 01 page 6 of 390 ...

Page 59: ...Rev 3 0 03 01 page 40 of 390 ...

Page 97: ...Rev 3 0 03 01 page 78 of 390 ...

Page 147: ...Rev 3 0 03 01 page 128 of 390 ...

Page 199: ...Rev 3 0 03 01 page 180 of 390 ...

Page 247: ...Rev 3 0 03 01 page 228 of 390 ...

Page 385: ...Rev 3 0 03 01 page 366 of 390 ...

Page 389: ...Rev 3 0 03 01 page 370 of 390 ...

Page 409: ...Rev 3 0 03 01 page 390 of 390 ...