Travelstar 5K80 Hard Disk Drive Specification

31

6.5 Vibration and shock

All vibration and shock measurements in this section are for drives without mounting attachments for systems. The

input level shall be applied to the normal drive mounting points.Vibration tests and shock tests are to be conducted

by mounting the drive to a table using the bottom four mounting holes.

6.5.1 Operating vibration

The drive will operate without a hard error while being subjected to the following vibration levels.

6.5.1.1 Random vibration

The test consists of 30 minutes of random vibration using the power spectral density (PSD) levels below. The

vibration test level is 6.57 m/sec

2

RMS (Root Mean Square) (0.67 G RMS).

6.5.1.2 Swept sine vibration

6.5.2 Nonoperating vibration

The disk drive withstands the vibration levels described below without any loss or permanent damage.

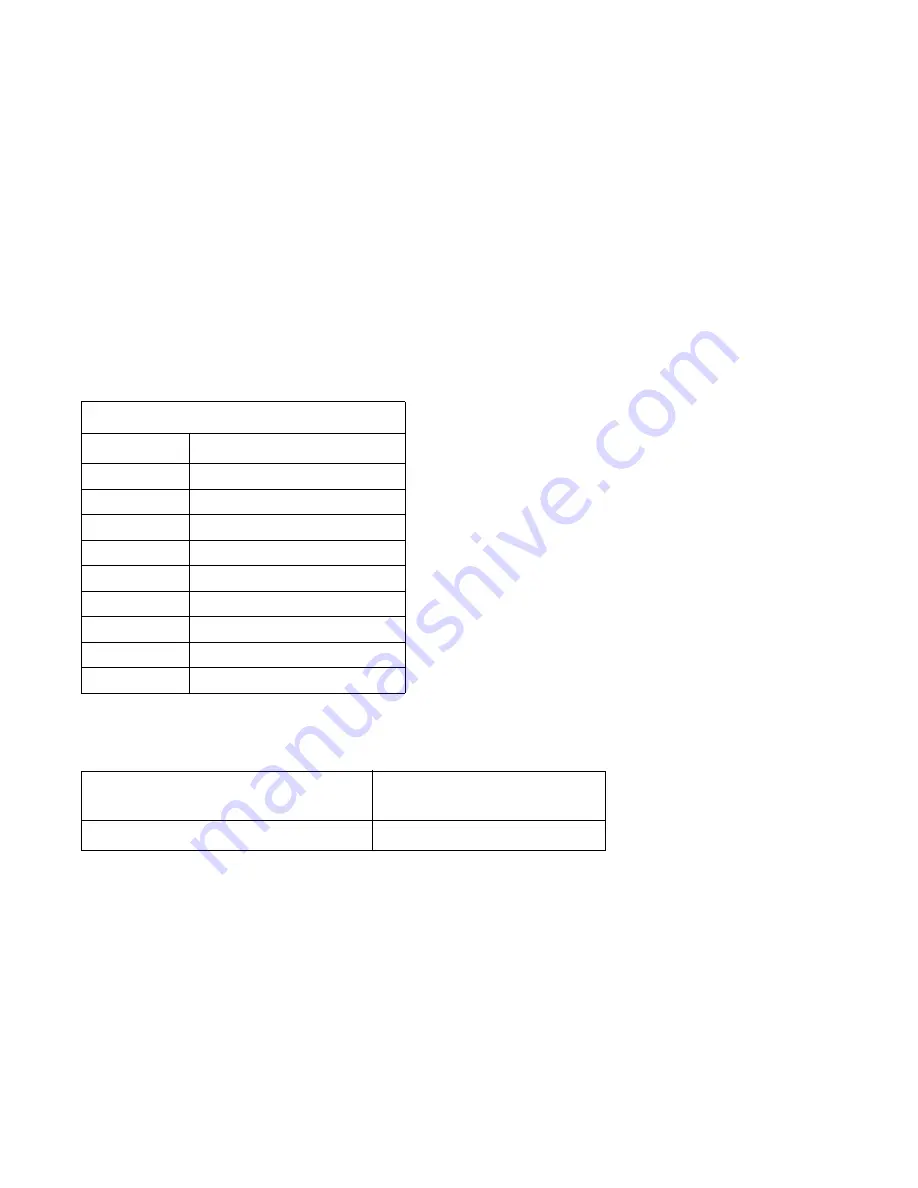

Table 18: Random vibration PSD profile breakpoints (operating)

Random vibration PSD profile breakpoint

Hz

m x 10n (m

2

/sec

4

)/Hz

5

1.9 x E–3

17

1.1 x E–1

45

1.1 x E–1

48

7.7 x E–1

62

7.7 x E–1

65

9.6 x E–1

150

9.6 x E–2

200

4.8x E–2

500

4.8 x E–2

Table 19: Swept sine vibration

Swept sine vibration

(zero to peak 5 to 500 to 5 Hz sine wave)

Sweep rate (oct/min)

9.8 m/sec

2

(1 G) (5-500 Hz)

2.0

Summary of Contents for HTS548020M9AT00

Page 2: ......

Page 14: ...Travelstar 5K80 Hard Disk Drive Specification x ...

Page 20: ...Travelstar 5K80 Hard Disk Drive Specification 6 ...

Page 21: ...Travelstar 5K80 Hard Disk Drive Specification 7 Part 1 Functional specification ...

Page 22: ...Travelstar 5K80 Hard Disk Drive Specification 8 ...

Page 24: ...Travelstar 5K80 Hard Disk Drive Specification 10 ...

Page 34: ...Travelstar 5K80 Hard Disk Drive Specification 20 ...

Page 50: ...Travelstar 5K80 Hard Disk Drive Specification 36 ...

Page 69: ...Travelstar 5K80 Hard Disk Drive Specification 53 Part 2 Interface specification ...

Page 70: ...Travelstar 5K80 Hard Disk Drive Specification 54 ...

Page 72: ...Travelstar 5K80 Hard Disk Drive Specification 56 ...

Page 74: ...Travelstar 5K80 Hard Disk Drive Specification 58 ...

Page 102: ...Travelstar 5K80 Hard Disk Drive Specification 86 ...

Page 108: ...Travelstar 5K80 Hard Disk Drive Specification page 92 ...

Page 209: ...Travelstar 5K80 Hard Disk Drive Specification 193 ...

Page 210: ...Travelstar 5K80 Hard Disk Drive Specification 194 ...