Rev. 3.0, 04/02, page 88 of 1064

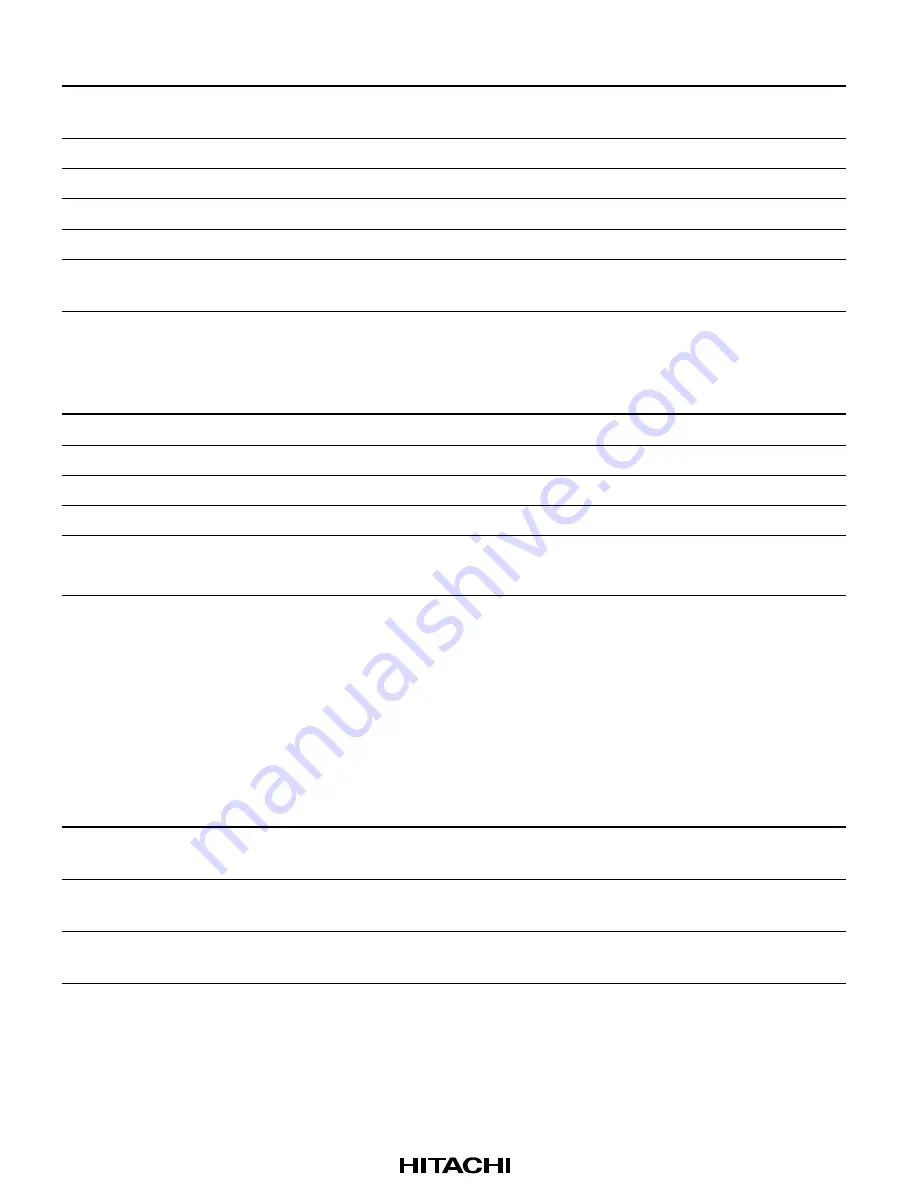

Table 4.2

Cache Features (SH7751R)

Item

Instruction Cache

Operand Cache

Capacity

16-kbyte cache

32-kbyte cache or 16-kbyte cache +

16-kbyte RAM

Type

2-way set-associative

2-way set-associative

Line size

32 bytes

32 bytes

Entries

256 entry/way

512 entry/way

Write method

Copy-back/write-through selectable

Replace method

LRU (Least Recently Used)

algorithm

LRU (Least Recently Used)

algorithm

Table 4.3

Store Queue Features

Item

Store Queues

Capacity

2

32 bytes

Addresses

H'E000 0000 to H'E3FF FFFF

Write

Store instruction (1-cycle write)

Write-back

Prefetch instruction (PREF instruction)

Access right

MMU off: according to MMUCR.SQMD

MMU on: according to individual page PR

4.1.2

Register Configuration

Table 4.4 shows the cache control registers.

Table 4.4

Cache Control Registers

Name

Abbreviation R/W

Initial

Value*

1

P4

Address*

2

Area 7

Address*

2

Access

Size

Cache control

register

CCR

R/W

H'0000 0000

H'FF00 001C

H'1F00 001C

32

Queue address

control register 0

QACR0

R/W

Undefined

H'FF00 0038

H'1F00 0038

32

Queue address

control register 1

QACR1

R/W

Undefined

H'FF00 003C

H'1F00 003C

32

Notes: *1 The initial value is the value after a power-on or manual reset.

*2 P4 address is the address when using the virtual/physical address space P4 area. The

area 7 address is the address used when making an access from physical address

space area 7 using the TLB.

Summary of Contents for SH7751

Page 39: ...Rev 3 0 04 02 page xxxviii of xxxviii ...

Page 89: ...Rev 3 0 04 02 page 50 of 1064 ...

Page 157: ...Rev 3 0 04 02 page 118 of 1064 ...

Page 193: ...Rev 3 0 04 02 page 154 of 1064 ...

Page 225: ...Rev 3 0 04 02 page 186 of 1064 ...

Page 253: ...Rev 3 0 04 02 page 214 of 1064 ...

Page 301: ...Rev 3 0 04 02 page 262 of 1064 ...

Page 343: ...Rev 3 0 04 02 page 304 of 1064 ...

Page 607: ...Rev 3 0 04 02 page 568 of 1064 ...

Page 671: ...Rev 3 0 04 02 page 632 of 1064 ...

Page 745: ...Rev 3 0 04 02 page 706 of 1064 ...

Page 767: ...Rev 3 0 04 02 page 728 of 1064 ...

Page 1061: ...Rev 3 0 04 02 page 1022 of 1064 NMI tNMIL tNMIH Figure 23 69 NMI Input Timing ...

Page 1069: ...Rev 3 0 04 02 page 1030 of 1064 ...

Page 1103: ...Rev 3 0 04 02 page 1064 of 1064 ...