Rev. 3.0, 04/02, page 203 of 1064

I

D

EX

NA

S

I

D

EX

NA

S

D

F1

F2

FS

D

F1

F2

FS

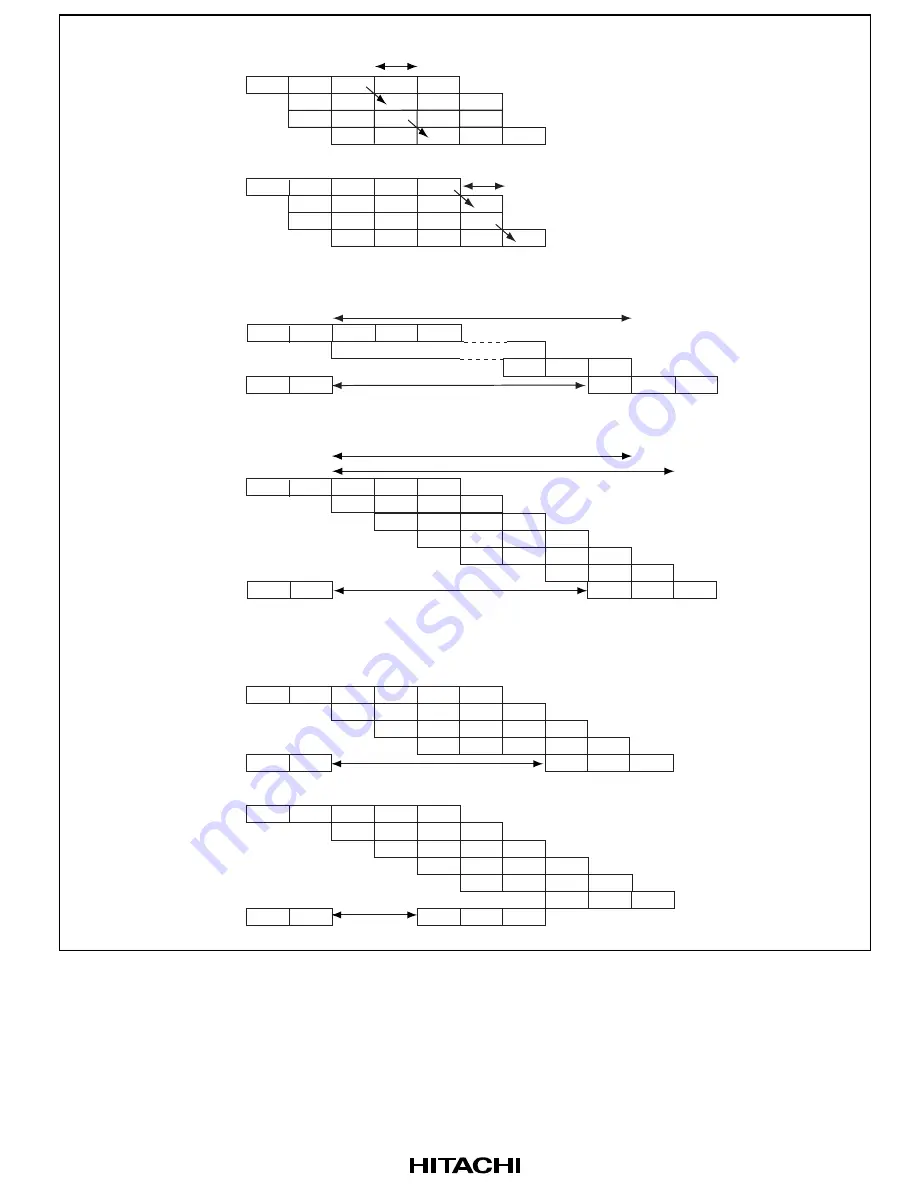

(e) Flow dependency (cont)

I

I

LDS

R0,FPUL

FLOAT FPUL,FR0

LDS

R1,FPUL

FLOAT FPUL,FR1

Effectively 1-cycle latency for consecutive LDS/FLOAT instructions

I

D

EX

NA

S

D

F1

F2

FS

I

D

F1

F2

FS

I

I

D

EX

NA

S

Effectively 1-cycle latency for consecutive

FTRC/STS instructions

FTRC

FR0,FPUL

STS

FPUL,R0

FTRC

FR1,FPUL

STS

FPUL,R1

(f) Output dependency

D

F1

F2

FS

I

I

D

F1

F2

FS

F1

F2

FS

11-cycle latency

10 stall cycles = latency (11) - 1

The registers are written-back

in program order.

D

F1

F2

FS

I

d

F1

F2

FS

d

F1

F2

FS

d

F1

F2

FS

d

F1

F2

FS

F1

F2

FS

EX

NA

S

I

D

7-cycle latency for lower FR

8-cycle latency for upper FR

6 stall cycles = longest latency (8) - 2

FR2 write

FR3 write

D

F1

F2

FS

I

d

F1

F2

FS

d

F1

F2

FS

d

F1

F0

F0

F0

F0

F2

FS

(g) Anti-flow dependency

EX

MA

S

I

D

5 stall cycles

D

F1

F2

FS

I

d

F1

F2

FS

d

F1

F2

FS

d

F1

F2

FS

EX

NA

S

I

D

2 stall cycles

d

F1

F2

FS

F1

F2

FS

FSQRT FR4

FMOV

FR0,FR4

FADD

DR0,DR2

FMOV

FR0,FR3

FTRV

XMTRX,FV0

FMOV @R1,XD0

FADD

DR0,DR2

FMOV FR4,FR1

F3

Figure 8.3 Examples of Pipelined Execution (cont)

Summary of Contents for SH7751

Page 39: ...Rev 3 0 04 02 page xxxviii of xxxviii ...

Page 89: ...Rev 3 0 04 02 page 50 of 1064 ...

Page 157: ...Rev 3 0 04 02 page 118 of 1064 ...

Page 193: ...Rev 3 0 04 02 page 154 of 1064 ...

Page 225: ...Rev 3 0 04 02 page 186 of 1064 ...

Page 253: ...Rev 3 0 04 02 page 214 of 1064 ...

Page 301: ...Rev 3 0 04 02 page 262 of 1064 ...

Page 343: ...Rev 3 0 04 02 page 304 of 1064 ...

Page 607: ...Rev 3 0 04 02 page 568 of 1064 ...

Page 671: ...Rev 3 0 04 02 page 632 of 1064 ...

Page 745: ...Rev 3 0 04 02 page 706 of 1064 ...

Page 767: ...Rev 3 0 04 02 page 728 of 1064 ...

Page 1061: ...Rev 3 0 04 02 page 1022 of 1064 NMI tNMIL tNMIH Figure 23 69 NMI Input Timing ...

Page 1069: ...Rev 3 0 04 02 page 1030 of 1064 ...

Page 1103: ...Rev 3 0 04 02 page 1064 of 1064 ...