Rev. 3.0, 04/02, page 396 of 1064

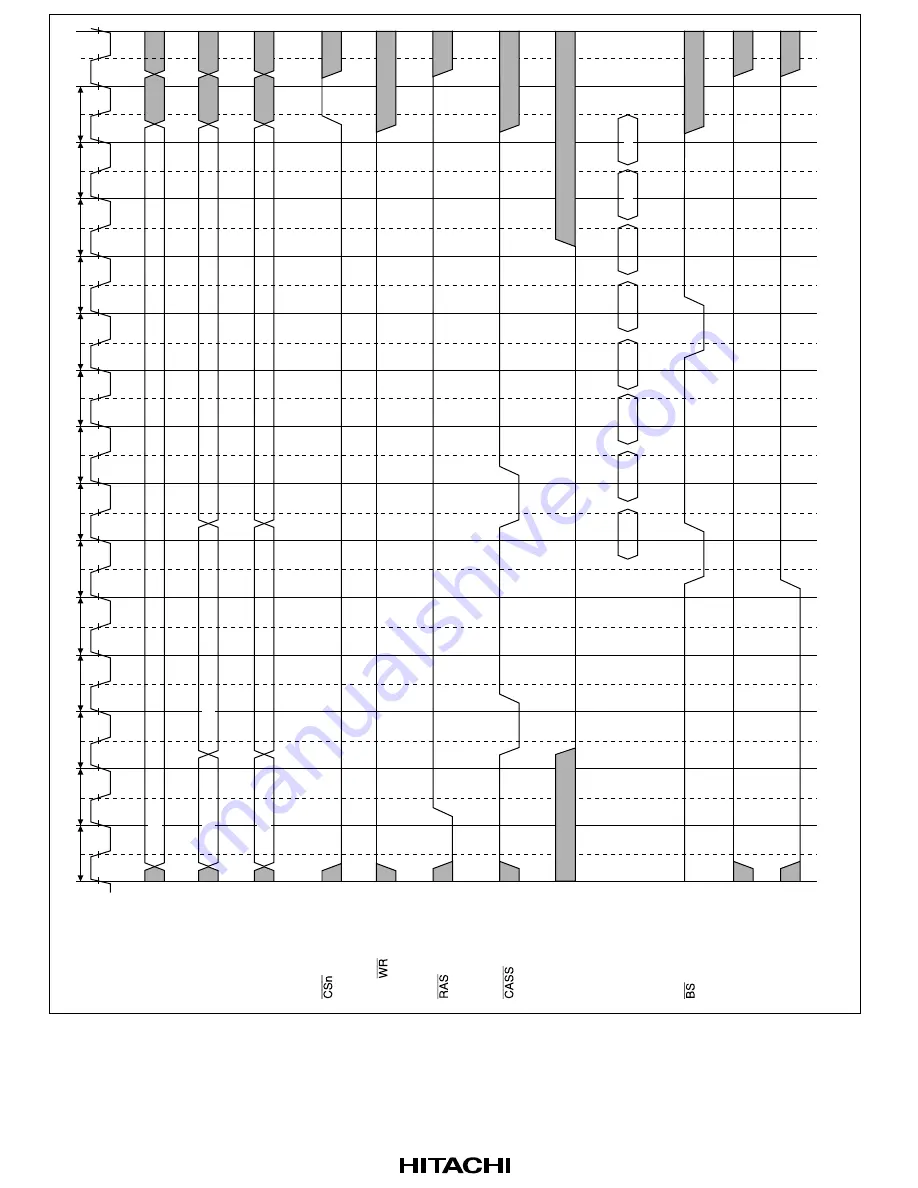

Tr

Trw

Tc1

Tc2

Tc3

Tc4/Td1

Td3

Td2

Td4

CKIO

Bank

Precharge-sel

Address

RD/

D31–D0

(read)

DQMn

DACKn

(SA: IO

←

memory)

CKE

H/L

c5

Td5

Td6

Td8

Td7

Tpc

c1

c1

c2

c3

c4

c5

c6

Row

Row

Row

c7

c8

H/L

Note:

F

or D

A

CKn, an e

xample is sho

wn where CHCRn.AL (access le

v

el) = 0 f

or the DMA

C

.

Figure 13.24 Basic Timing for Synchronous DRAM Burst Read

Summary of Contents for SH7751

Page 39: ...Rev 3 0 04 02 page xxxviii of xxxviii ...

Page 89: ...Rev 3 0 04 02 page 50 of 1064 ...

Page 157: ...Rev 3 0 04 02 page 118 of 1064 ...

Page 193: ...Rev 3 0 04 02 page 154 of 1064 ...

Page 225: ...Rev 3 0 04 02 page 186 of 1064 ...

Page 253: ...Rev 3 0 04 02 page 214 of 1064 ...

Page 301: ...Rev 3 0 04 02 page 262 of 1064 ...

Page 343: ...Rev 3 0 04 02 page 304 of 1064 ...

Page 607: ...Rev 3 0 04 02 page 568 of 1064 ...

Page 671: ...Rev 3 0 04 02 page 632 of 1064 ...

Page 745: ...Rev 3 0 04 02 page 706 of 1064 ...

Page 767: ...Rev 3 0 04 02 page 728 of 1064 ...

Page 1061: ...Rev 3 0 04 02 page 1022 of 1064 NMI tNMIL tNMIH Figure 23 69 NMI Input Timing ...

Page 1069: ...Rev 3 0 04 02 page 1030 of 1064 ...

Page 1103: ...Rev 3 0 04 02 page 1064 of 1064 ...