Rev. 3.0, 04/02, page 691 of 1064

(Z)

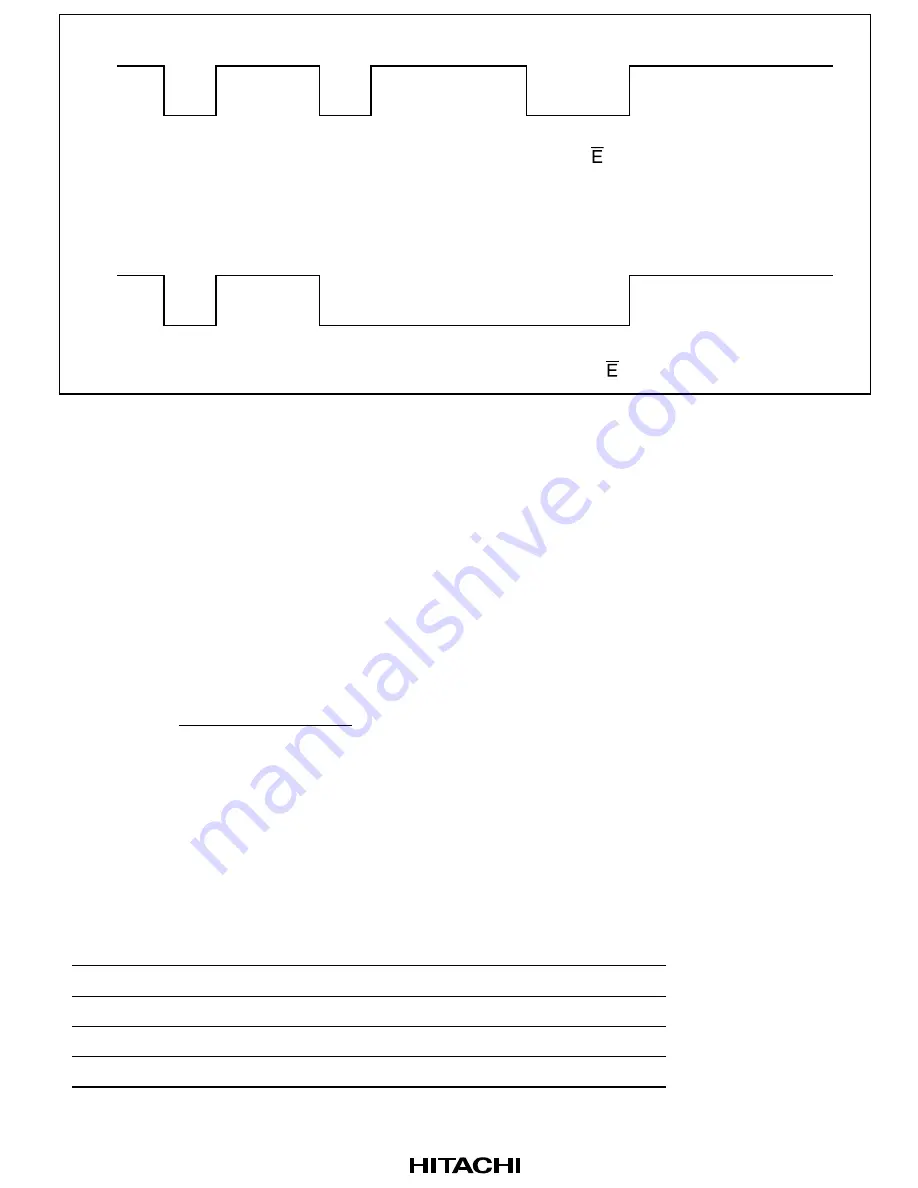

(a) Direct convention (SDIR = SINV = O/ = 0)

(b) Inverse convention (SDIR = SINV = O/ = 1)

A

Z

Z

A

Z

Z

Z

A

A

Z

(Z)

State

Ds

D0

D1

D2

D3

D4

D5

D6

D7

Dp

(Z)

A

Z

Z

A

A

A

A

A

A

Z

(Z)

State

Ds

D7

D6

D5

D4

D3

D2

D1

D0

Dp

Figure 17.5 Sample Start Character Waveforms

17.3.5

Clock

Only an internal clock generated by the on-chip baud rate generator can be used as the

transmit/receive clock for the smart card interface. The bit rate is set with the bit rate register

(SCBRR1) and the CKS1 and CKS0 bits in the serial mode register (SCSMR1). The equation for

calculating the bit rate is shown below. Table 17.5 shows some sample bit rates.

If clock output is selected with CKE0 set to 1, a clock with a frequency of 372 times the bit rate is

output from the SCK pin.

B =

×

10

6

1488

×

2

2n–1

×

(N + 1)

φ

P

Where: N = Value set in SCBRR1 (0

N 255)

B = Bit rate (bits/s)

P

= Peripheral module operating frequency (MHz)

n = 0 to 3 (See table 17.4)

Table 17.4

Values of n and Corresponding CKS1 and CKS0 Settings

n

CKS1

CKS0

0

0

0

1

0

1

2

1

0

3

1

1

Summary of Contents for SH7751

Page 39: ...Rev 3 0 04 02 page xxxviii of xxxviii ...

Page 89: ...Rev 3 0 04 02 page 50 of 1064 ...

Page 157: ...Rev 3 0 04 02 page 118 of 1064 ...

Page 193: ...Rev 3 0 04 02 page 154 of 1064 ...

Page 225: ...Rev 3 0 04 02 page 186 of 1064 ...

Page 253: ...Rev 3 0 04 02 page 214 of 1064 ...

Page 301: ...Rev 3 0 04 02 page 262 of 1064 ...

Page 343: ...Rev 3 0 04 02 page 304 of 1064 ...

Page 607: ...Rev 3 0 04 02 page 568 of 1064 ...

Page 671: ...Rev 3 0 04 02 page 632 of 1064 ...

Page 745: ...Rev 3 0 04 02 page 706 of 1064 ...

Page 767: ...Rev 3 0 04 02 page 728 of 1064 ...

Page 1061: ...Rev 3 0 04 02 page 1022 of 1064 NMI tNMIL tNMIH Figure 23 69 NMI Input Timing ...

Page 1069: ...Rev 3 0 04 02 page 1030 of 1064 ...

Page 1103: ...Rev 3 0 04 02 page 1064 of 1064 ...