Rev. 3.0, 04/02, page 722 of 1064

18.2.4

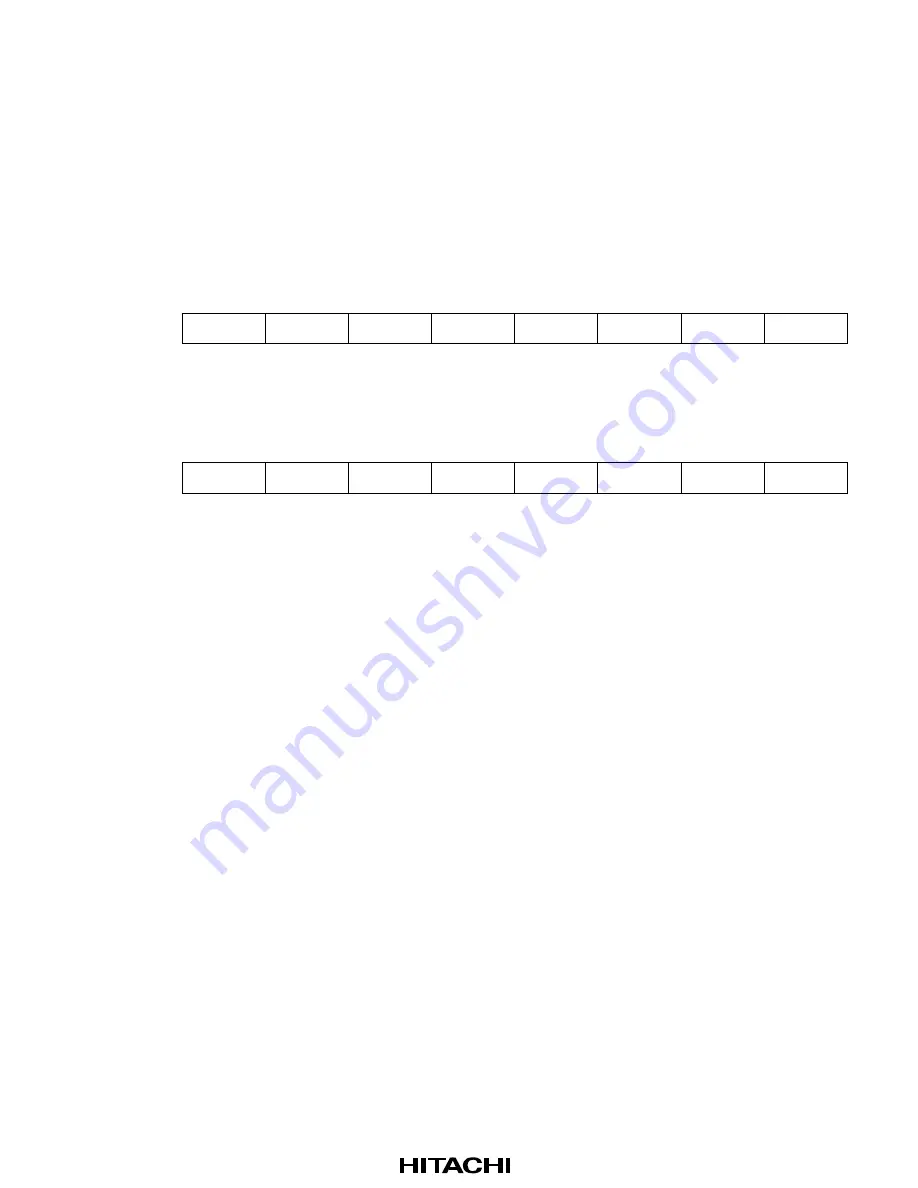

Port Data Register B (PDTRB)

Port data register B (PDTRB) is a 16-bit readable/writable register used as a data latch for each bit

in the 16-bit port B. When a bit is set as an output, the value written to the PDTRB register is

output from the external pin. When a value is read from the PDTRB register while a bit is set as an

input, the external pin value sampled on the external bus clock is read. When a bit is set as an

output, the value written to the PDTRB register is read.

PDTRB is not initialized by a power-on or manual reset, or in standby mode, and retains its

contents.

Bit:

15

14

13

12

11

10

9

8

PB31DT PB30DT PB29DT PB28DT PB27DT PB26DT PB25DT PB24DT

Initial value:

—

—

—

—

—

—

—

—

R/W:

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

Bit:

7

6

5

4

3

2

1

0

PB23DT PB22DT PB21DT PB20DT PB19DT PB18DT PB17DT PB16DT

Initial value:

—

—

—

—

—

—

—

—

R/W:

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

18.2.5

GPIO Interrupt Control Register (GPIOIC)

The GPIO interrupt control register (GPIOIC) is a 16-bit readable/writable register that performs

16-bit interrupt input control.

GPIOIC is initialized to H'0000 by a power-on reset. It is not initialized by a manual reset or in

standby mode, and retains its contents.

GPIO interrupts are active-low level interrupts. Bit-by-bit masking is possible, and the OR of all

the bits set as GPIO interrupts is used for interrupt detection. Which bits interrupts are input to can

be identified by reading the PDTRA register.

Summary of Contents for SH7751

Page 39: ...Rev 3 0 04 02 page xxxviii of xxxviii ...

Page 89: ...Rev 3 0 04 02 page 50 of 1064 ...

Page 157: ...Rev 3 0 04 02 page 118 of 1064 ...

Page 193: ...Rev 3 0 04 02 page 154 of 1064 ...

Page 225: ...Rev 3 0 04 02 page 186 of 1064 ...

Page 253: ...Rev 3 0 04 02 page 214 of 1064 ...

Page 301: ...Rev 3 0 04 02 page 262 of 1064 ...

Page 343: ...Rev 3 0 04 02 page 304 of 1064 ...

Page 607: ...Rev 3 0 04 02 page 568 of 1064 ...

Page 671: ...Rev 3 0 04 02 page 632 of 1064 ...

Page 745: ...Rev 3 0 04 02 page 706 of 1064 ...

Page 767: ...Rev 3 0 04 02 page 728 of 1064 ...

Page 1061: ...Rev 3 0 04 02 page 1022 of 1064 NMI tNMIL tNMIH Figure 23 69 NMI Input Timing ...

Page 1069: ...Rev 3 0 04 02 page 1030 of 1064 ...

Page 1103: ...Rev 3 0 04 02 page 1064 of 1064 ...