Rev. 3.0, 04/02, page 723 of 1064

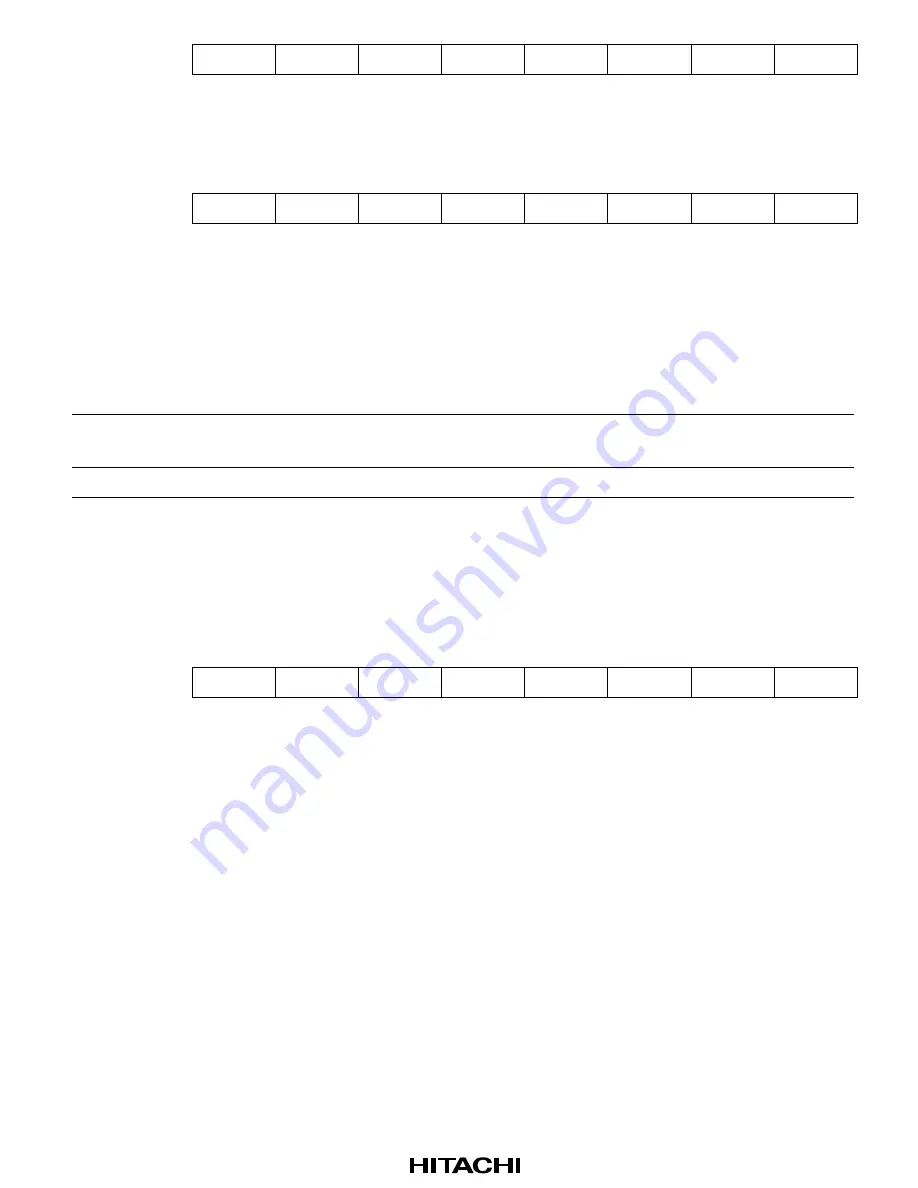

Bit:

15

14

13

12

11

10

9

8

PTIREN15 PTIREN14 PTIREN13 PTIREN12 PTIREN11 PTIREN10 PTIREN9

PTIREN8

Initial value:

0

0

0

0

0

0

0

0

R/W:

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

Bit:

7

6

5

4

3

2

1

0

PTIREN7

PTIREN6

PTIREN5

PTIREN4

PTIREN3

PTIREN2

PTIREN1

PTIREN0

Initial value:

0

0

0

0

0

0

0

0

R/W:

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

Bit n (n = 0–15)—Port Interrupt Enable (PTIRENn): Specifies whether interrupt input is

performed for each bit.

Bit n: PTIRENn

Description

0

Port m (m = 0–15) of 16-bit port A is used as a normal I/O port

(Initial value)

1

Port m (m = 0–15) of 16-bit port A is used as a GPIO interrupt*

Note: * When using an interrupt, set the corresponding port to input in the PCTRA register before

making the PTIRENn setting.

18.2.6

Serial Port Register (SCSPTR1)

Bit:

7

6

5

4

3

2

1

0

EIO

—

—

—

SPB1IO SPB1DT SPB0IO SPB0DT

Initial value:

0

0

0

0

0

—

0

—

R/W:

R/W

—

—

—

R/W

R/W

R/W

R/W

The serial port register (SCSPTR1) is an 8-bit readable/writable register that controls input/output

and data for the port pins multiplexed with the serial communication interface (SCI) pins. Input

data can be read from the RxD pin, output data written to the TxD pin, and breaks in serial

transmission/reception controlled, by means of bits 1 and 0. SCK pin data reading and output data

writing can be performed by means of bits 3 and 2. Bit 7 controls enabling and disabling of the

RXI interrupt.

SCSPTR1 can be read or written to by the CPU at all times. All SCSPTR1 bits except bits 2 and 0

are initialized to 0 by a power-on reset or manual reset; the value of bits 2 and 0 is undefined.

SCSPTR1 is not initialized in the module standby state or standby mode.

Bit 7—Error Interrupt Only (EIO): See section 15.2.8, Serial Port Register (SCSPTR1).

Bits 6 to 4—Reserved: These bits are always read as 0, and should only be written with 0.

Summary of Contents for SH7751

Page 39: ...Rev 3 0 04 02 page xxxviii of xxxviii ...

Page 89: ...Rev 3 0 04 02 page 50 of 1064 ...

Page 157: ...Rev 3 0 04 02 page 118 of 1064 ...

Page 193: ...Rev 3 0 04 02 page 154 of 1064 ...

Page 225: ...Rev 3 0 04 02 page 186 of 1064 ...

Page 253: ...Rev 3 0 04 02 page 214 of 1064 ...

Page 301: ...Rev 3 0 04 02 page 262 of 1064 ...

Page 343: ...Rev 3 0 04 02 page 304 of 1064 ...

Page 607: ...Rev 3 0 04 02 page 568 of 1064 ...

Page 671: ...Rev 3 0 04 02 page 632 of 1064 ...

Page 745: ...Rev 3 0 04 02 page 706 of 1064 ...

Page 767: ...Rev 3 0 04 02 page 728 of 1064 ...

Page 1061: ...Rev 3 0 04 02 page 1022 of 1064 NMI tNMIL tNMIH Figure 23 69 NMI Input Timing ...

Page 1069: ...Rev 3 0 04 02 page 1030 of 1064 ...

Page 1103: ...Rev 3 0 04 02 page 1064 of 1064 ...