Rev. 3.0, 04/02, page 730 of 1064

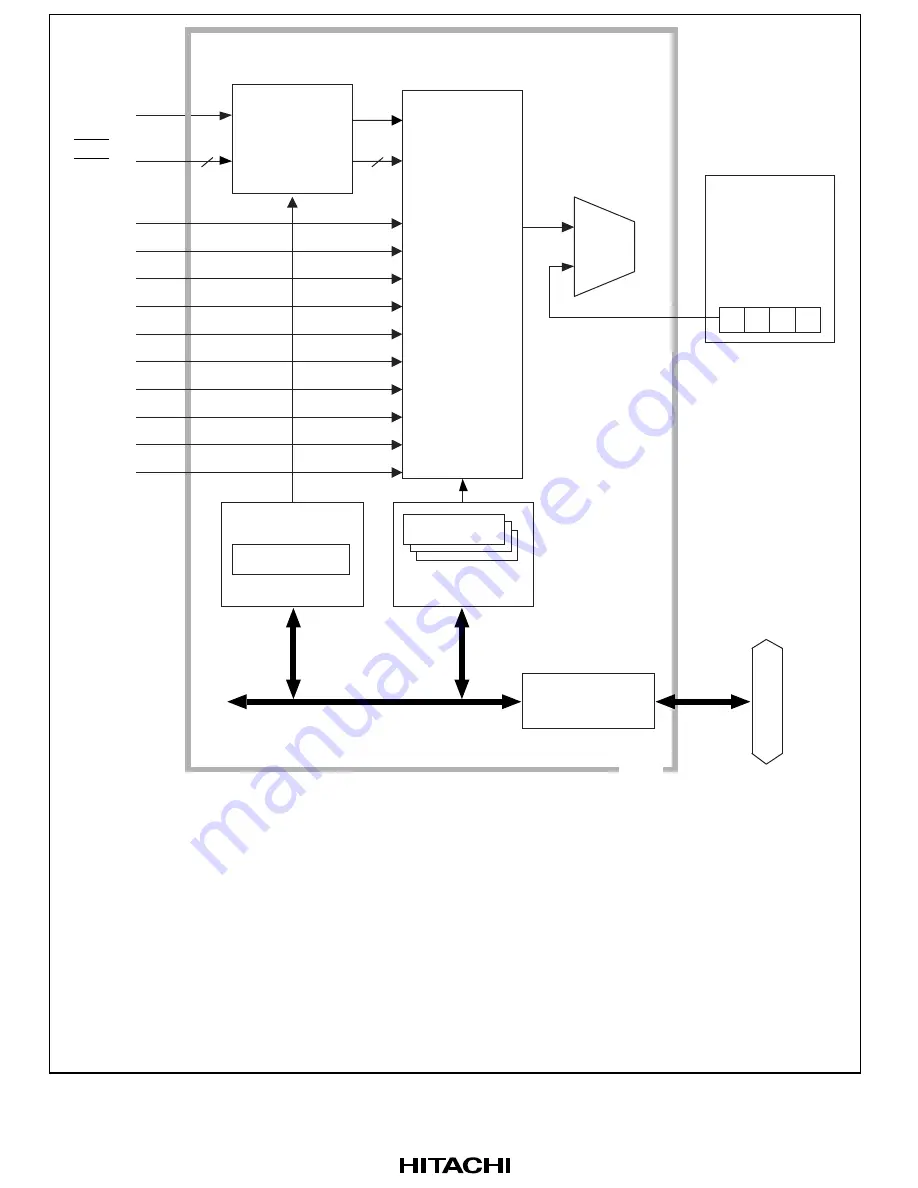

TMU:

Timer unit

RTC:

Realtime clock unit

SCI:

Serial communication interface

SCIF:

Serial communication interface with FIFO

WDT: Watchdog

timer

REF:

Memory refresh controller section of the bus state controller

DMAC:

Direct memory access controller

H-UDI:

Hitachi user debug interface unit

GPIO:

I/O port

PCIC:

PCI bus controller

ICR:

Interrupt control register

IPRA–IPRD: Interrupt priority registers A–D

INTPRI00:

Interrupt priority register 00

SR: Status

register

NMI

Input control

IRL3–

IRL0

TMU

RTC

SCI

SCIF

WDT

REF

DMAC

H-UDI

Priority

identifier

4

4

(Interrupt request)

Com-

parator

Bus interface

Internal bus

ICR

IPRA–IPRD,

INTPRI00

(Interrupt request)

(Interrupt request)

(Interrupt request)

(Interrupt request)

(Interrupt request)

(Interrupt request)

(Interrupt request)

(Interrupt request)

INTC

Interrupt

request

I3 I2 I1 I0

SR

CPU

IPR

GPIO

(Interrupt request)

PCIC

Figure 19.1 Block Diagram of INTC

Summary of Contents for SH7751

Page 39: ...Rev 3 0 04 02 page xxxviii of xxxviii ...

Page 89: ...Rev 3 0 04 02 page 50 of 1064 ...

Page 157: ...Rev 3 0 04 02 page 118 of 1064 ...

Page 193: ...Rev 3 0 04 02 page 154 of 1064 ...

Page 225: ...Rev 3 0 04 02 page 186 of 1064 ...

Page 253: ...Rev 3 0 04 02 page 214 of 1064 ...

Page 301: ...Rev 3 0 04 02 page 262 of 1064 ...

Page 343: ...Rev 3 0 04 02 page 304 of 1064 ...

Page 607: ...Rev 3 0 04 02 page 568 of 1064 ...

Page 671: ...Rev 3 0 04 02 page 632 of 1064 ...

Page 745: ...Rev 3 0 04 02 page 706 of 1064 ...

Page 767: ...Rev 3 0 04 02 page 728 of 1064 ...

Page 1061: ...Rev 3 0 04 02 page 1022 of 1064 NMI tNMIL tNMIH Figure 23 69 NMI Input Timing ...

Page 1069: ...Rev 3 0 04 02 page 1030 of 1064 ...

Page 1103: ...Rev 3 0 04 02 page 1064 of 1064 ...