Rev. 3.0, 04/02, page 734 of 1064

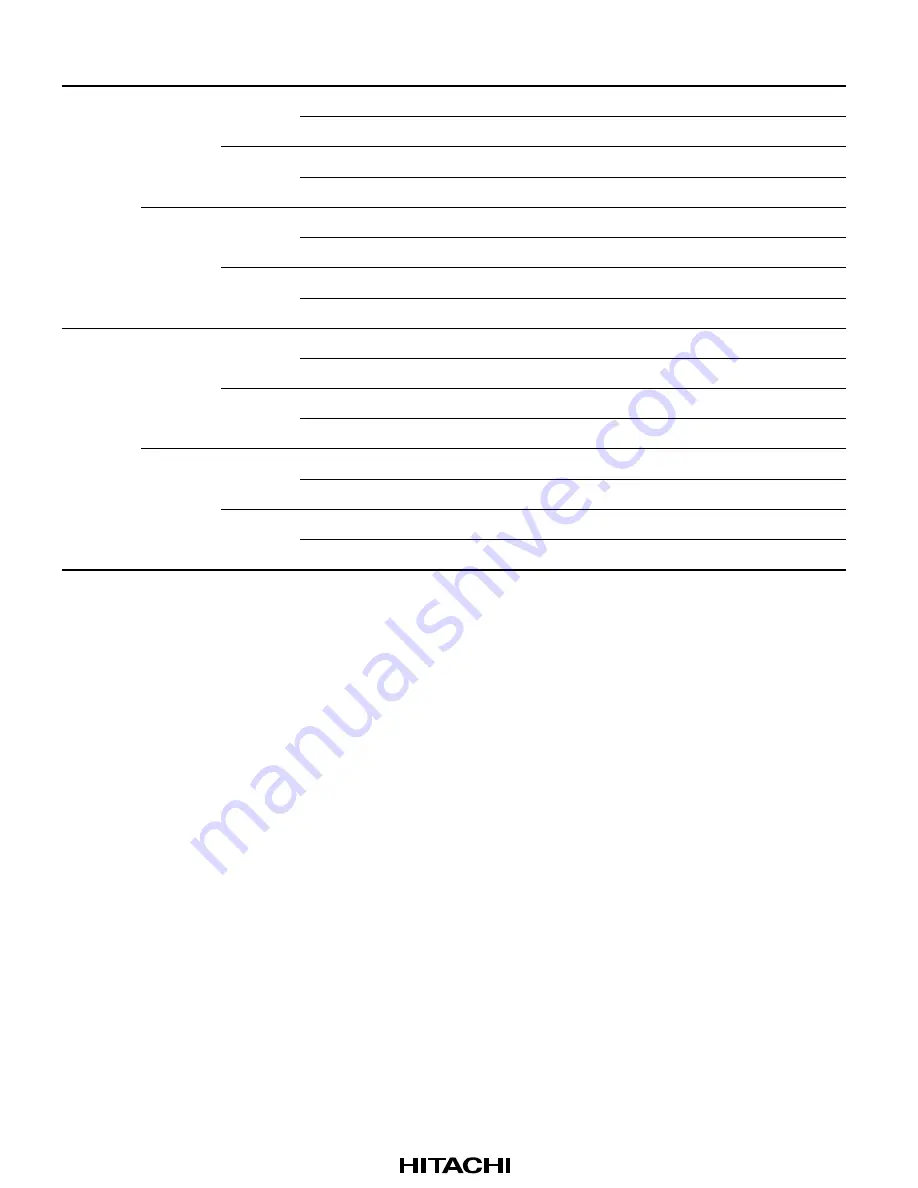

Table 19.3

–

Pins and Interrupt Levels

Interrupt Priority Level

Interrupt Request

0

0

0

0

15

Level 15 interrupt request

1

14

Level 14 interrupt request

1

0

13

Level 13 interrupt request

1

12

Level 12 interrupt request

1

0

0

11

Level 11 interrupt request

1

10

Level 10 interrupt request

1

0

9

Level 9 interrupt request

1

8

Level 8 interrupt request

1

0

0

0

7

Level 7 interrupt request

1

6

Level 6 interrupt request

1

0

5

Level 5 interrupt request

1

4

Level 4 interrupt request

1

0

0

3

Level 3 interrupt request

1

2

Level 2 interrupt request

1

0

1

Level 1 interrupt request

1

0

No interrupt request

A noise-cancellation feature is built in, and the IRL interrupt is not detected unless the levels

sampled at every bus clock cycle remain unchanged for three consecutive cycles, so that no

transient level on the

pin change is detected. In standby mode, as the bus clock is stopped,

noise cancellation is performed using the 32.768 kHz clock for the RTC instead. When the RTC is

not used, therefore, interruption by means of IRL interrupts cannot be performed in standby mode.

The priority level of the IRL interrupt must not be lowered unless the interrupt is accepted and the

interrupt handling starts. However, the priority level can be changed to a higher one.

The interrupt mask bits (I3–I0) in the status register (SR) are not affected by IRL interrupt

handling.

Pins

– can be used for four independent interrupt requests by setting the IRLM bit to 1

in the ICR register.

Summary of Contents for SH7751

Page 39: ...Rev 3 0 04 02 page xxxviii of xxxviii ...

Page 89: ...Rev 3 0 04 02 page 50 of 1064 ...

Page 157: ...Rev 3 0 04 02 page 118 of 1064 ...

Page 193: ...Rev 3 0 04 02 page 154 of 1064 ...

Page 225: ...Rev 3 0 04 02 page 186 of 1064 ...

Page 253: ...Rev 3 0 04 02 page 214 of 1064 ...

Page 301: ...Rev 3 0 04 02 page 262 of 1064 ...

Page 343: ...Rev 3 0 04 02 page 304 of 1064 ...

Page 607: ...Rev 3 0 04 02 page 568 of 1064 ...

Page 671: ...Rev 3 0 04 02 page 632 of 1064 ...

Page 745: ...Rev 3 0 04 02 page 706 of 1064 ...

Page 767: ...Rev 3 0 04 02 page 728 of 1064 ...

Page 1061: ...Rev 3 0 04 02 page 1022 of 1064 NMI tNMIL tNMIH Figure 23 69 NMI Input Timing ...

Page 1069: ...Rev 3 0 04 02 page 1030 of 1064 ...

Page 1103: ...Rev 3 0 04 02 page 1064 of 1064 ...