Rev. 3.0, 04/02, page 744 of 1064

19.3.5

Interrupt Mask Register 00 (INTMSK00)

The interrupt mask register 00 (INTMSK00) specifies whether or not to mask individual interrupts

each time they are requested. The INTMSK00 register is a 32-bit register. It is initialized to

H'000003FF at a reset. The values are retained in standby mode.

To clear each interrupt mask, write 1 to the corresponding bit of the INTMSKCLR00 register. The

values in INTMSK00 do not change if you write 0 to it.

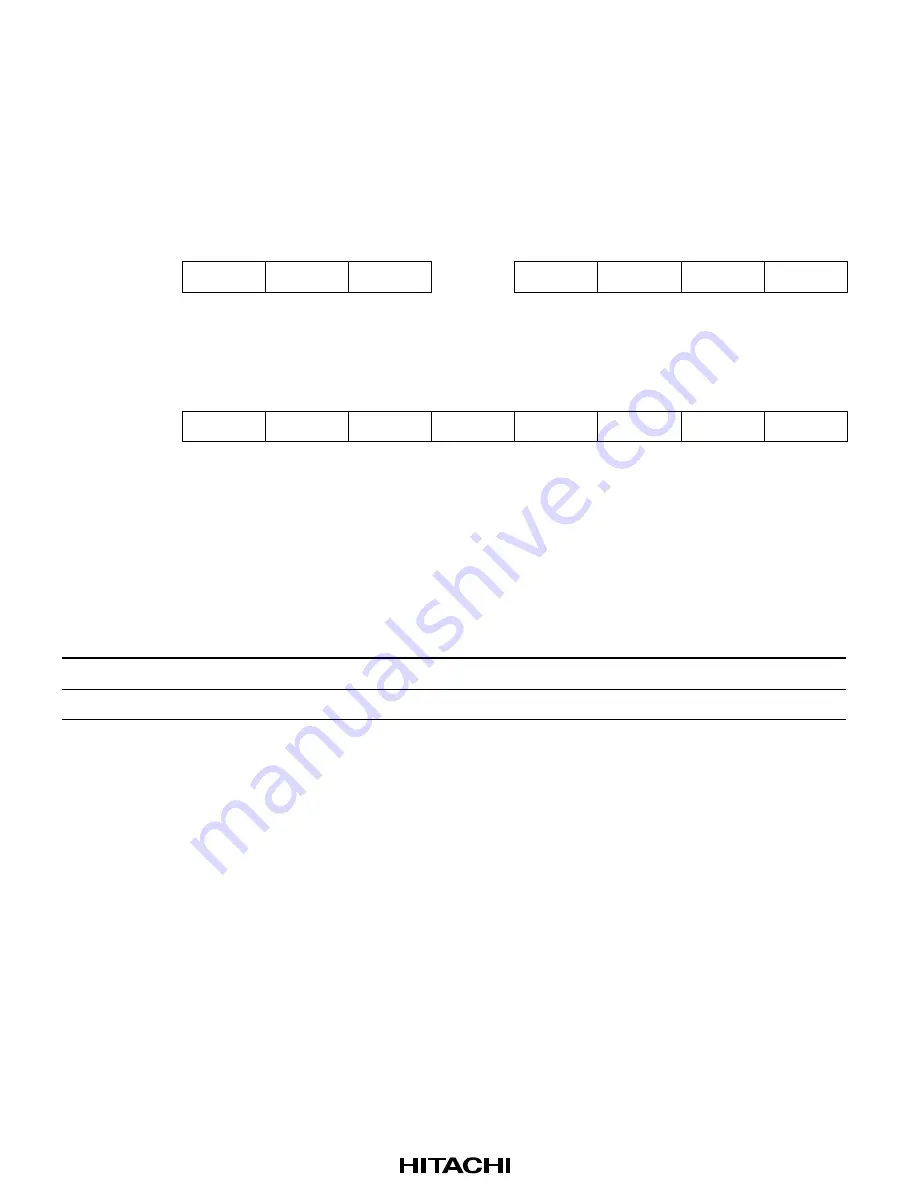

Bit:

31

30

29

. . .

11

10

9

8

. . .

Initial value:

0

0

0

. . .

0

0

1

1

R/W:

R

R

R

. . .

R

R

R/W

R/W

Bit:

7

6

5

4

3

2

1

0

Initial value:

1

1

1

1

1

1

1

1

R/W:

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

Bits 31 to 0—Interrupt Masks: These bits indicate the existence of an interrupt request

corresponding to each bit. For the correspondence between bits and interrupt sources, see section

19.3.7, INTREQ00, INTMSK00, and INTMSKCLR00 Bit Allocation.

Bits 31 to 0

Description

0

Accept corresponding interrupt request

1

Mask corresponding interrupt request

(Initial value)

Summary of Contents for SH7751

Page 39: ...Rev 3 0 04 02 page xxxviii of xxxviii ...

Page 89: ...Rev 3 0 04 02 page 50 of 1064 ...

Page 157: ...Rev 3 0 04 02 page 118 of 1064 ...

Page 193: ...Rev 3 0 04 02 page 154 of 1064 ...

Page 225: ...Rev 3 0 04 02 page 186 of 1064 ...

Page 253: ...Rev 3 0 04 02 page 214 of 1064 ...

Page 301: ...Rev 3 0 04 02 page 262 of 1064 ...

Page 343: ...Rev 3 0 04 02 page 304 of 1064 ...

Page 607: ...Rev 3 0 04 02 page 568 of 1064 ...

Page 671: ...Rev 3 0 04 02 page 632 of 1064 ...

Page 745: ...Rev 3 0 04 02 page 706 of 1064 ...

Page 767: ...Rev 3 0 04 02 page 728 of 1064 ...

Page 1061: ...Rev 3 0 04 02 page 1022 of 1064 NMI tNMIL tNMIH Figure 23 69 NMI Input Timing ...

Page 1069: ...Rev 3 0 04 02 page 1030 of 1064 ...

Page 1103: ...Rev 3 0 04 02 page 1064 of 1064 ...