Rev. 3.0, 04/02, page 748 of 1064

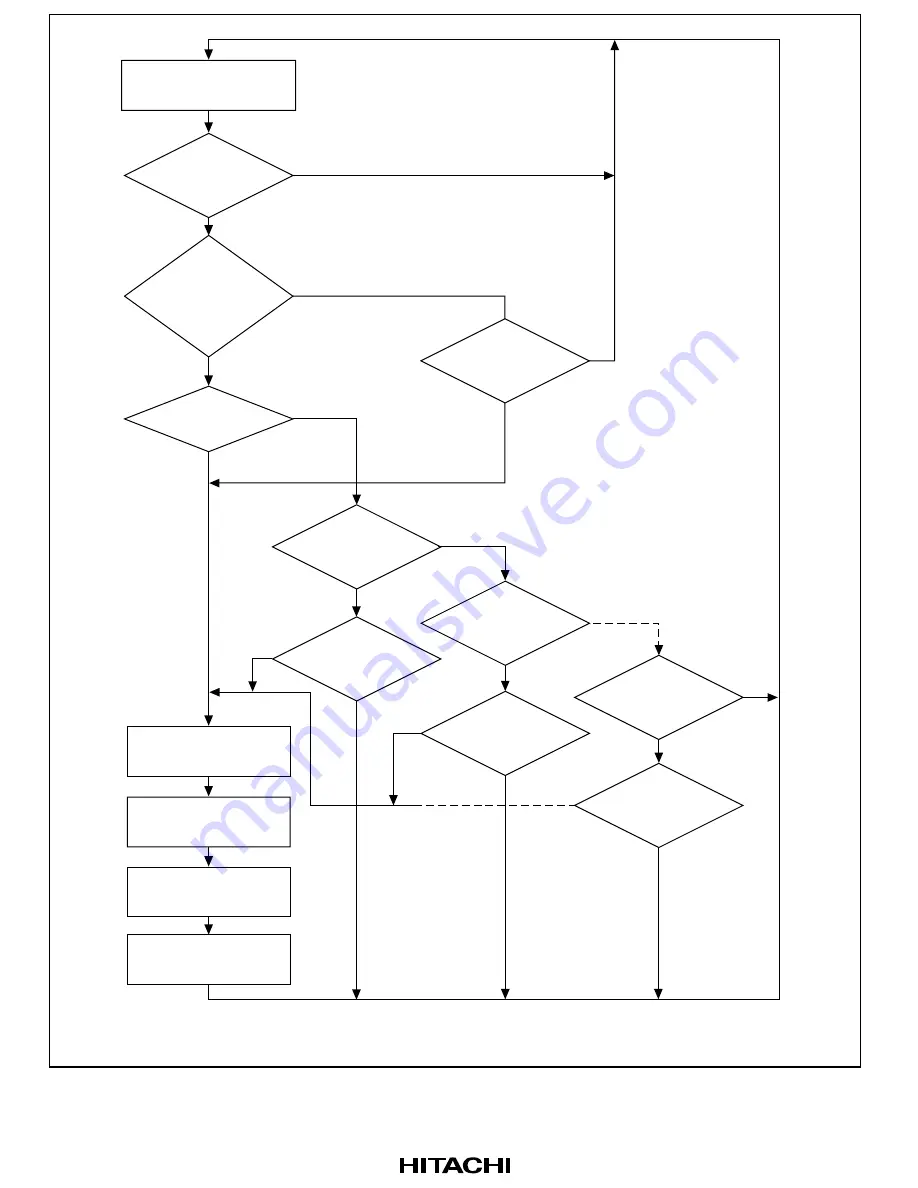

Program

execution state

No

No

Yes

No

Yes

No

Yes

Yes

No

No

Yes

Yes

No

Yes

No

No

Yes

No

Yes

Save SR to SSR;

save PC to SPC

Set interrupt source

in INTEVT

Set BL, MD, RB bits

in SR to 1

Branch to exception

handler

Interrupt

generated?

(BL bit

in SR = 0) or

(sleep or standby

mode)?

NMI?

Level 14

interrupt?

Level 1

interrupt?

I3–I0 =

level 13 or

lower?

I3–I0 =

level 0?

Yes

Level 15

interrupt?

I3–I0* =

level 14 or

lower?

Note: * I3–I0: Interrupt mask bits in status register (SR)

NMIB in

ICR = 1 and

NMI?

Figure 19.3 Interrupt Operation Flowchart

Summary of Contents for SH7751

Page 39: ...Rev 3 0 04 02 page xxxviii of xxxviii ...

Page 89: ...Rev 3 0 04 02 page 50 of 1064 ...

Page 157: ...Rev 3 0 04 02 page 118 of 1064 ...

Page 193: ...Rev 3 0 04 02 page 154 of 1064 ...

Page 225: ...Rev 3 0 04 02 page 186 of 1064 ...

Page 253: ...Rev 3 0 04 02 page 214 of 1064 ...

Page 301: ...Rev 3 0 04 02 page 262 of 1064 ...

Page 343: ...Rev 3 0 04 02 page 304 of 1064 ...

Page 607: ...Rev 3 0 04 02 page 568 of 1064 ...

Page 671: ...Rev 3 0 04 02 page 632 of 1064 ...

Page 745: ...Rev 3 0 04 02 page 706 of 1064 ...

Page 767: ...Rev 3 0 04 02 page 728 of 1064 ...

Page 1061: ...Rev 3 0 04 02 page 1022 of 1064 NMI tNMIL tNMIH Figure 23 69 NMI Input Timing ...

Page 1069: ...Rev 3 0 04 02 page 1030 of 1064 ...

Page 1103: ...Rev 3 0 04 02 page 1064 of 1064 ...