Rev. 3.0, 04/02, page 761 of 1064

Bits 31 to 0—Break Data Mask B31 to B0 (BDMB31–BDMB0): These bits specify whether the

corresponding bit of the channel B break data (BDB31–BDB0) set in BDRB is to be masked.

Bit 31–0: BDMBn

Description

0

Channel B break data bit BDBn is included in break conditions

1

Channel B break data bit BDBn is masked, and not included in break

conditions

n = 31 to 0

Note:

When the data bus value is included in the break conditions, the operand size should be

specified. When byte size is specified, set the same data in bits 15–8 and 7–0 of BDRB and

BDMRB.

20.2.11

Break Bus Cycle Register B (BBRB)

BBRB is the channel B bus break register. The bit configuration is the same as for BBRA.

20.2.12

Break Control Register (BRCR)

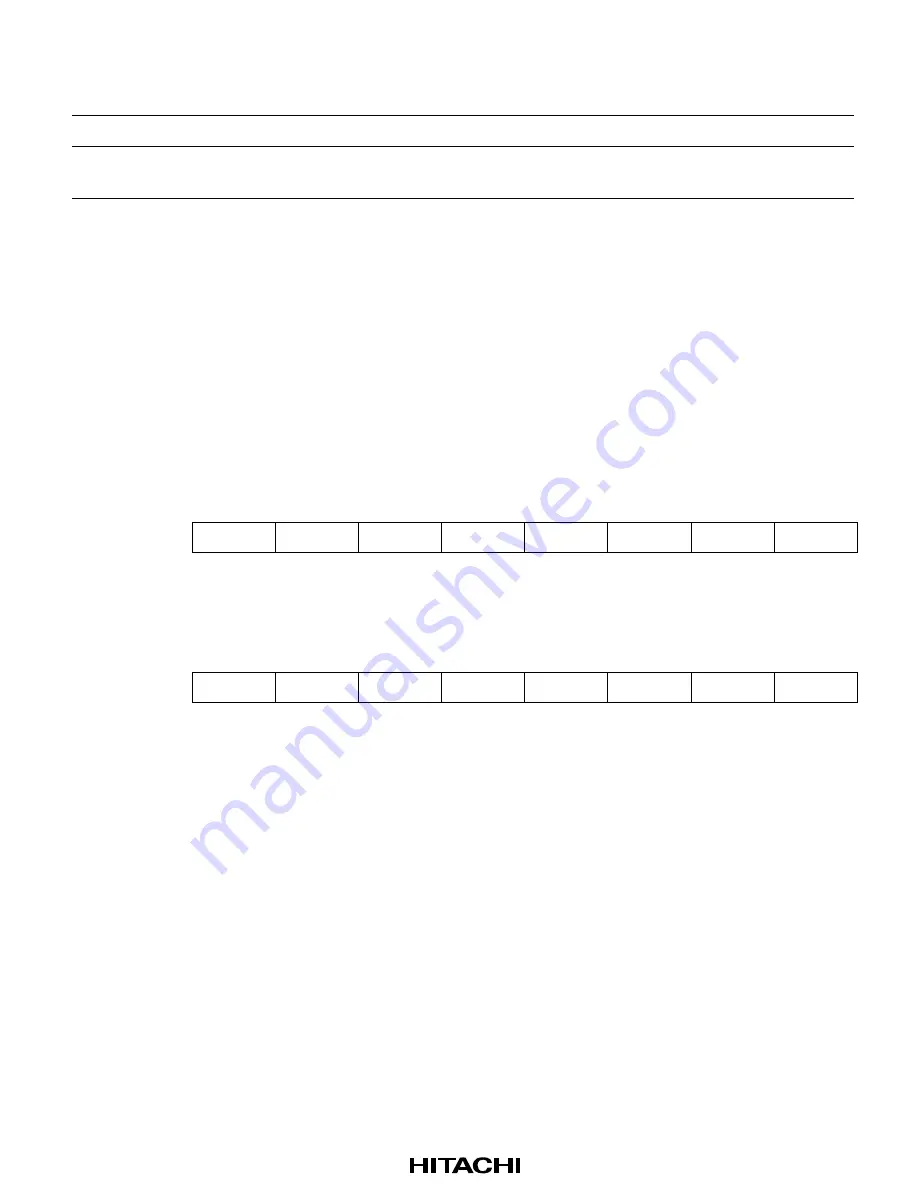

Bit:

15

14

13

12

11

10

9

8

CMFA

CMFB

—

—

—

PCBA

—

—

Initial value:

0

0

0

0

0

*

0

0

R/W:

R/W

R/W

R

R

R

R/W

R

R

Bit:

7

6

5

4

3

2

1

0

DBEB

PCBB

—

—

SEQ

—

—

UBDE

Initial value:

*

*

0

0

*

0

0

0

R/W:

R/W

R/W

R

R

R/W

R

R

R/W

Note:

*

: Undefined

The break control register (BRCR) is a 16-bit readable/writable register that specifies (1) whether

channels A and B are to be used as two independent channels or in a sequential condition, (2)

whether the break is to be effected before or after instruction execution, (3) whether the BDRB

register is to be included in the channel B break conditions, and (4) whether the user break debug

function is to be used. BRCR also contains condition match flags. The CMFA, CMFB, and UBDE

bits in BRCR are initialized to 0 by a power-on reset, but retain their value in standby mode. The

value of the PCBA, DBEB, PCBB, and SEQ bits is undefined after a power-on reset or manual

reset, so these bits should be initialized by software as necessary.

Summary of Contents for SH7751

Page 39: ...Rev 3 0 04 02 page xxxviii of xxxviii ...

Page 89: ...Rev 3 0 04 02 page 50 of 1064 ...

Page 157: ...Rev 3 0 04 02 page 118 of 1064 ...

Page 193: ...Rev 3 0 04 02 page 154 of 1064 ...

Page 225: ...Rev 3 0 04 02 page 186 of 1064 ...

Page 253: ...Rev 3 0 04 02 page 214 of 1064 ...

Page 301: ...Rev 3 0 04 02 page 262 of 1064 ...

Page 343: ...Rev 3 0 04 02 page 304 of 1064 ...

Page 607: ...Rev 3 0 04 02 page 568 of 1064 ...

Page 671: ...Rev 3 0 04 02 page 632 of 1064 ...

Page 745: ...Rev 3 0 04 02 page 706 of 1064 ...

Page 767: ...Rev 3 0 04 02 page 728 of 1064 ...

Page 1061: ...Rev 3 0 04 02 page 1022 of 1064 NMI tNMIL tNMIH Figure 23 69 NMI Input Timing ...

Page 1069: ...Rev 3 0 04 02 page 1030 of 1064 ...

Page 1103: ...Rev 3 0 04 02 page 1064 of 1064 ...