Rev. 3.0, 04/02, page 782 of 1064

21.2.2

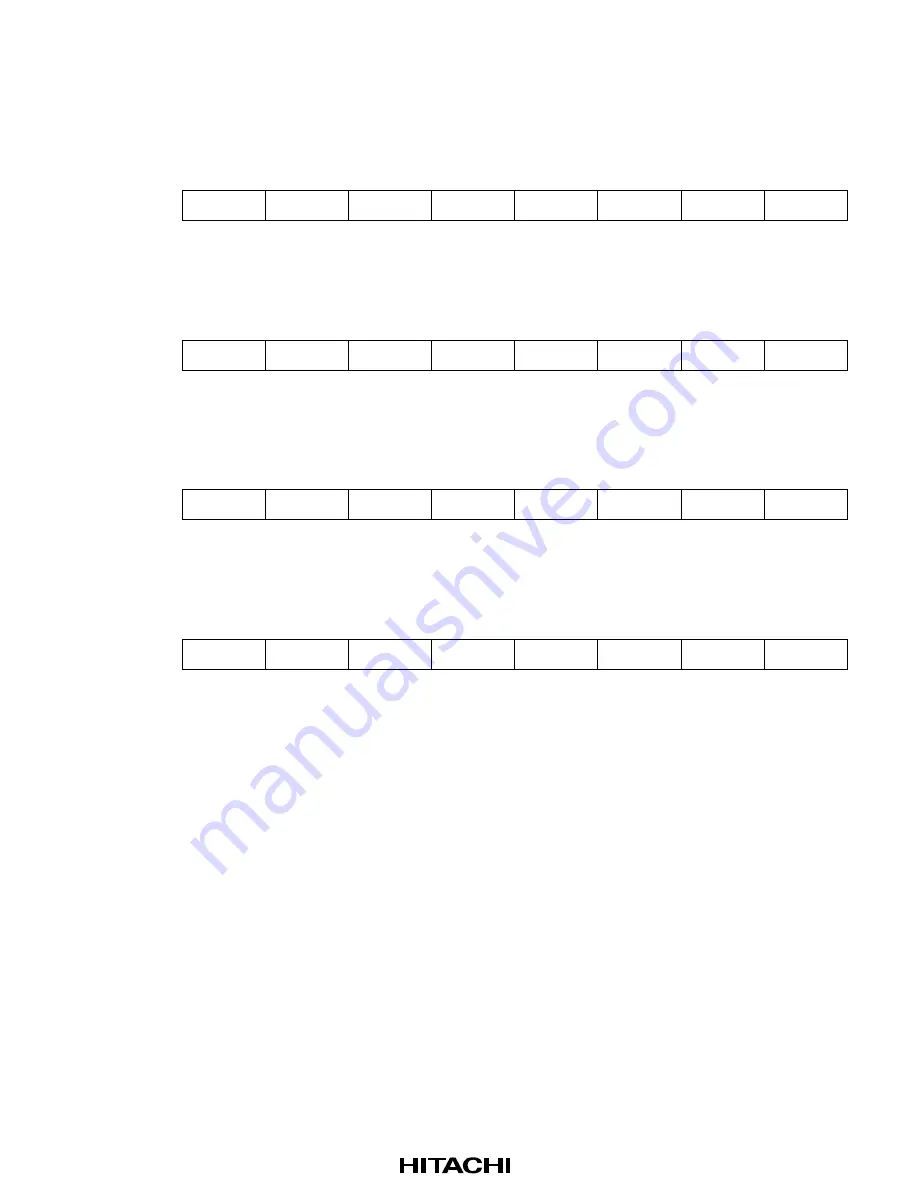

Data Register (SDDR)

The data register (SDDR) is a 32-bit register, comprising the two 16-bit registers SDDRH and

SDDRL, that can be read and written to by the CPU. The value in this register is initialized by

, but not by a CPU reset.

Bit:

31

30

29

28

27

26

25

24

Initial value:

*

*

*

*

*

*

*

*

R/W:

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

Bit:

23

22

21

20

19

18

17

16

Initial value:

*

*

*

*

*

*

*

*

R/W:

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

Bit:

15

14

13

12

11

10

9

8

Initial value:

*

*

*

*

*

*

*

*

R/W:

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

Bit:

7

6

5

4

3

2

1

0

Initial value:

*

*

*

*

*

*

*

*

R/W:

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

Note:

*

: Undefined

Bits 31 to 0—DR Data: These bits store the SDDR value.

21.2.3

Bypass Register (SDBPR)

The bypass register (SDBPR) is a one-bit register that cannot be accessed by the CPU. When

bypass mode is set in SDIR, SDBPR is connected between the TDI pin and TDO pin of the

H-UDI.

Summary of Contents for SH7751

Page 39: ...Rev 3 0 04 02 page xxxviii of xxxviii ...

Page 89: ...Rev 3 0 04 02 page 50 of 1064 ...

Page 157: ...Rev 3 0 04 02 page 118 of 1064 ...

Page 193: ...Rev 3 0 04 02 page 154 of 1064 ...

Page 225: ...Rev 3 0 04 02 page 186 of 1064 ...

Page 253: ...Rev 3 0 04 02 page 214 of 1064 ...

Page 301: ...Rev 3 0 04 02 page 262 of 1064 ...

Page 343: ...Rev 3 0 04 02 page 304 of 1064 ...

Page 607: ...Rev 3 0 04 02 page 568 of 1064 ...

Page 671: ...Rev 3 0 04 02 page 632 of 1064 ...

Page 745: ...Rev 3 0 04 02 page 706 of 1064 ...

Page 767: ...Rev 3 0 04 02 page 728 of 1064 ...

Page 1061: ...Rev 3 0 04 02 page 1022 of 1064 NMI tNMIL tNMIH Figure 23 69 NMI Input Timing ...

Page 1069: ...Rev 3 0 04 02 page 1030 of 1064 ...

Page 1103: ...Rev 3 0 04 02 page 1064 of 1064 ...