Rev. 3.0, 04/02, page 853 of 1064

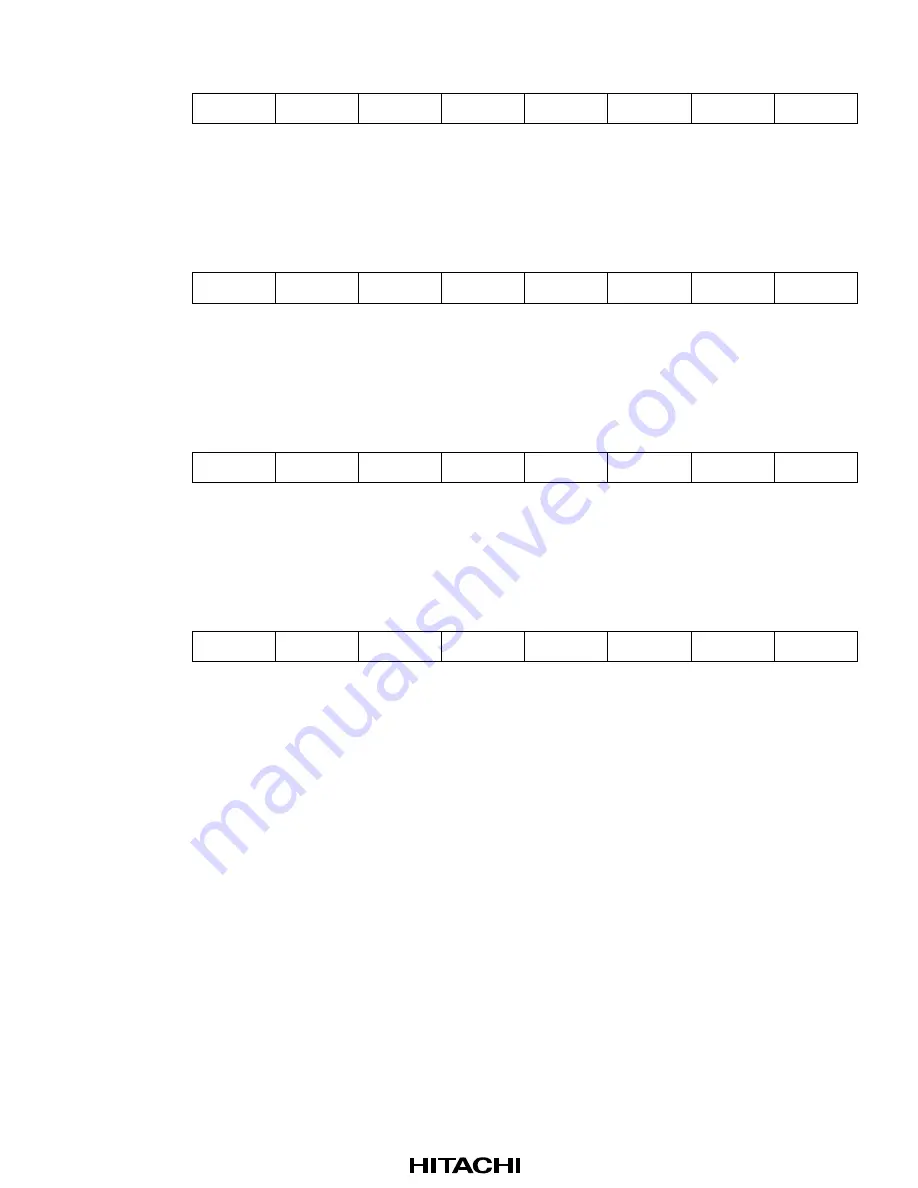

22.2.24

PCI Arbiter Interrupt Register (PCIAINT)

Bit:

31

30

29

28

27

26

25

24

—

—

—

—

—

—

—

—

Initial value:

0

0

0

0

0

0

0

0

PCI-R/W:

R

R

R

R

R

R

R

R

PP Bus-R/W:

R

R

R

R

R

R

R

R

Bit:

23

22

21

20

19

18

17

16

—

—

—

—

—

—

—

—

Initial value:

0

0

0

0

0

0

0

0

PCI-R/W:

R

R

R

R

R

R

R

R

PP Bus-R/W:

R

R

R

R

R

R

R

R

Bit:

15

14

13

12

11

10

9

8

—

—

MST_BRKN

TGT_BUSTO

MST_BUSTO

—

—

—

Initial value:

0

0

0

0

0

0

0

0

PCI-R/W:

R

R

R/WC

R/WC

R/WC

R

R

R

PP Bus-R/W:

R

R

R/WC

R/WC

R/WC

R

R

R

Bit:

7

6

5

4

3

2

1

0

—

—

—

—

TGT_ABORT

MST_ABORT

DPERR_WT

DPERR_RD

Initial value:

0

0

0

0

0

0

0

0

PCI-R/W:

R

R

R

R

R/WC

R/WC

R/WC

R/WC

PP Bus-R/W:

R

R

R

R

R/WC

R/WC

R/WC

R/WC

Note:

Cleared by writing WC:1. (Writing of 0 is ignored.)

The PCI arbiter interrupt register (PCIAINT) is a 32-bit register that stores the sources of PCI bus

errors occurring during transfers by another PCI master device when the PCIC is operating as the

host with the arbitration function. The register can be read from both the PP bus and the PCI bus.

Also, each interrupt detection bit can be cleared to its initial status (0) by writing 1 to it from either

the PP bus or the PCI bus. (Write clear)

The PCIINT register is initialized to H'00000000 at a power-on reset or software reset.

When an error is detected, the bit corresponding to the error type is set to 1. Each interrupt

detection bit can be cleared to its initial status (0) by writing 1 to it. (Write clear)

The error detection bits are set even when the interrupts are masked.

Summary of Contents for SH7751

Page 39: ...Rev 3 0 04 02 page xxxviii of xxxviii ...

Page 89: ...Rev 3 0 04 02 page 50 of 1064 ...

Page 157: ...Rev 3 0 04 02 page 118 of 1064 ...

Page 193: ...Rev 3 0 04 02 page 154 of 1064 ...

Page 225: ...Rev 3 0 04 02 page 186 of 1064 ...

Page 253: ...Rev 3 0 04 02 page 214 of 1064 ...

Page 301: ...Rev 3 0 04 02 page 262 of 1064 ...

Page 343: ...Rev 3 0 04 02 page 304 of 1064 ...

Page 607: ...Rev 3 0 04 02 page 568 of 1064 ...

Page 671: ...Rev 3 0 04 02 page 632 of 1064 ...

Page 745: ...Rev 3 0 04 02 page 706 of 1064 ...

Page 767: ...Rev 3 0 04 02 page 728 of 1064 ...

Page 1061: ...Rev 3 0 04 02 page 1022 of 1064 NMI tNMIL tNMIH Figure 23 69 NMI Input Timing ...

Page 1069: ...Rev 3 0 04 02 page 1030 of 1064 ...

Page 1103: ...Rev 3 0 04 02 page 1064 of 1064 ...