Rev. 3.0, 04/02, page 856 of 1064

Bit 11—Master Bus Timeout Interrupt Mask (MST_BUSTO)

Bits 10 to 4—Reserved: These bits always return 0 when read. Always write 0 to these bits when

writing.

Bit 3—Target Abort Interrupt Mask (TGT_ABORT)

Bit 2—Master Abort interrupt Mask (MST_ABORT)

Bit 1—Read Data Parity Error Interrupt Mask (DPERR_WT)

Bit 0—Write Data Parity Error Interrupt Mask (DPERR_RD)

22.2.26

PCI Error Bus Master Data Register (PCIBMLR)

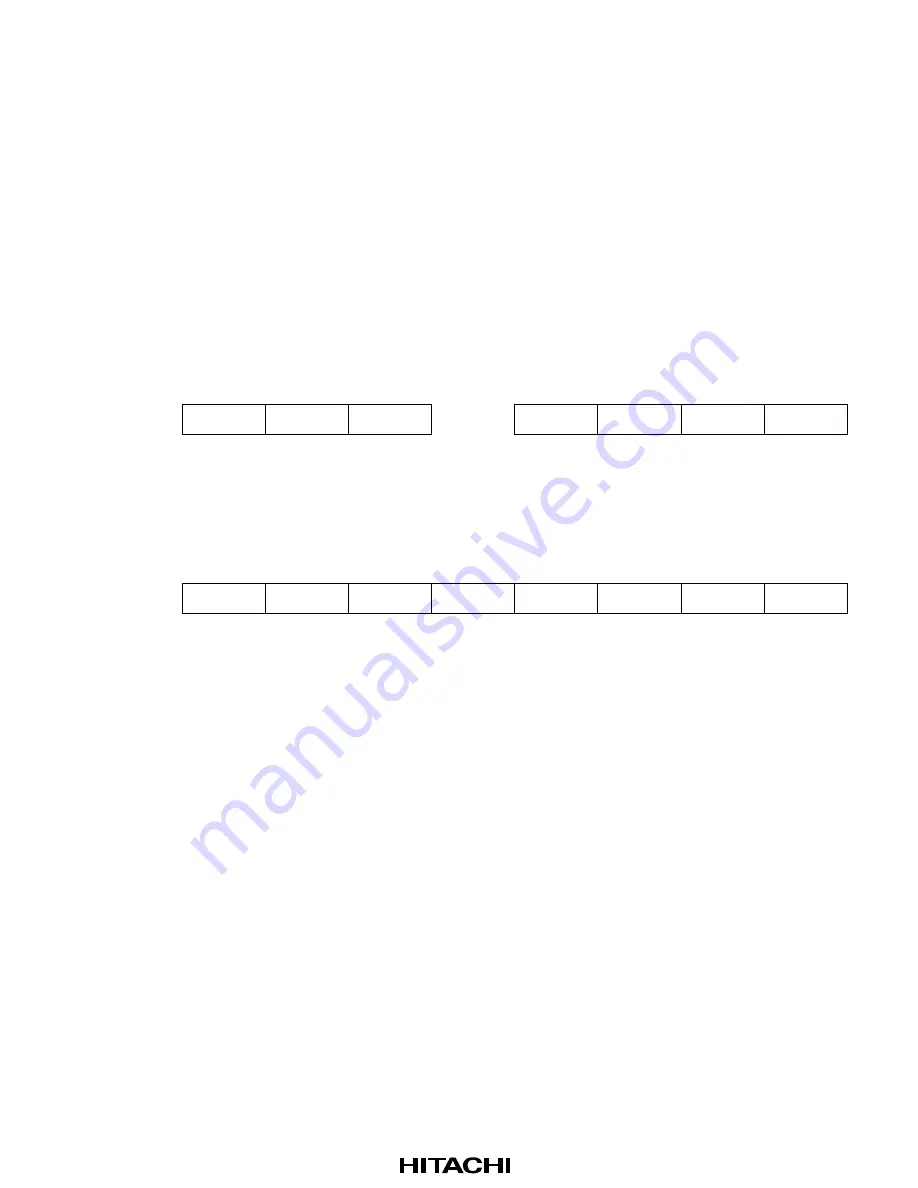

Bit:

31

30

29

. . .

11

10

9

8

—

—

—

. . .

—

—

—

—

Initial value:

0

0

0

. . .

0

0

0

0

PCI-R/W:

R

R

R

. . .

R

R

R

R

PP Bus-R/W:

R

R

R

. . .

R

R

R

R

Bit:

7

6

5

4

3

2

1

0

—

—

—

REQ4ID

REQ3ID

REQ2ID

REQ1ID

REQ0ID

Initial value:

0

0

0

—

—

—

—

—

PCI-R/W:

R

R

R

R

R

R

R

R

PP Bus-R/W:

R

R

R

R

R

R

R

R

The PCI error bus master data register (PCIBMLR) stores the device number of the bus master at

the time an error occurred in PCI transfer by another PCI device when the PCIC was operating as

the host with the arbitration function. It is a 32-bit register than can be read from both the PP bus

and PCI bus.

The PCIINTM register is initialized to H'00000000 at a power-on reset or software reset. A valid

value is retained only when one of the PCIAINT register bits is set to 1.

The bus master data holding circuit can only store data for one master. For this reason, no bus

master data is stored for any second or subsequent errors if errors occur consecutively.

Bits 31 to 5—Reserved: These bits always return 0 when read. Always write 0 to these bits when

writing.

Bit 4—REQ4 Error (REQ4ID): Error occurred when device 4 (REQ4) was bus master.

Summary of Contents for SH7751

Page 39: ...Rev 3 0 04 02 page xxxviii of xxxviii ...

Page 89: ...Rev 3 0 04 02 page 50 of 1064 ...

Page 157: ...Rev 3 0 04 02 page 118 of 1064 ...

Page 193: ...Rev 3 0 04 02 page 154 of 1064 ...

Page 225: ...Rev 3 0 04 02 page 186 of 1064 ...

Page 253: ...Rev 3 0 04 02 page 214 of 1064 ...

Page 301: ...Rev 3 0 04 02 page 262 of 1064 ...

Page 343: ...Rev 3 0 04 02 page 304 of 1064 ...

Page 607: ...Rev 3 0 04 02 page 568 of 1064 ...

Page 671: ...Rev 3 0 04 02 page 632 of 1064 ...

Page 745: ...Rev 3 0 04 02 page 706 of 1064 ...

Page 767: ...Rev 3 0 04 02 page 728 of 1064 ...

Page 1061: ...Rev 3 0 04 02 page 1022 of 1064 NMI tNMIL tNMIH Figure 23 69 NMI Input Timing ...

Page 1069: ...Rev 3 0 04 02 page 1030 of 1064 ...

Page 1103: ...Rev 3 0 04 02 page 1064 of 1064 ...