Rev. 3.0, 04/02, page 868 of 1064

Bits 31 to 24—Memory Space Base Address (MBR31 to 24): Sets the base address for the PCI

memory space in PIO transfers. (Initial value is undefined.)

Bits 23 to 1—Reserved: These bits always return 0 when read. Always write 0 to these bits when

writing.

Bit 0—Lock Transfer (LOCK): Specifies the locking of the memory space during PIO transfer.

Bit 0: LOCK

Description

0

Not locked

(Initial value)

1

Locked

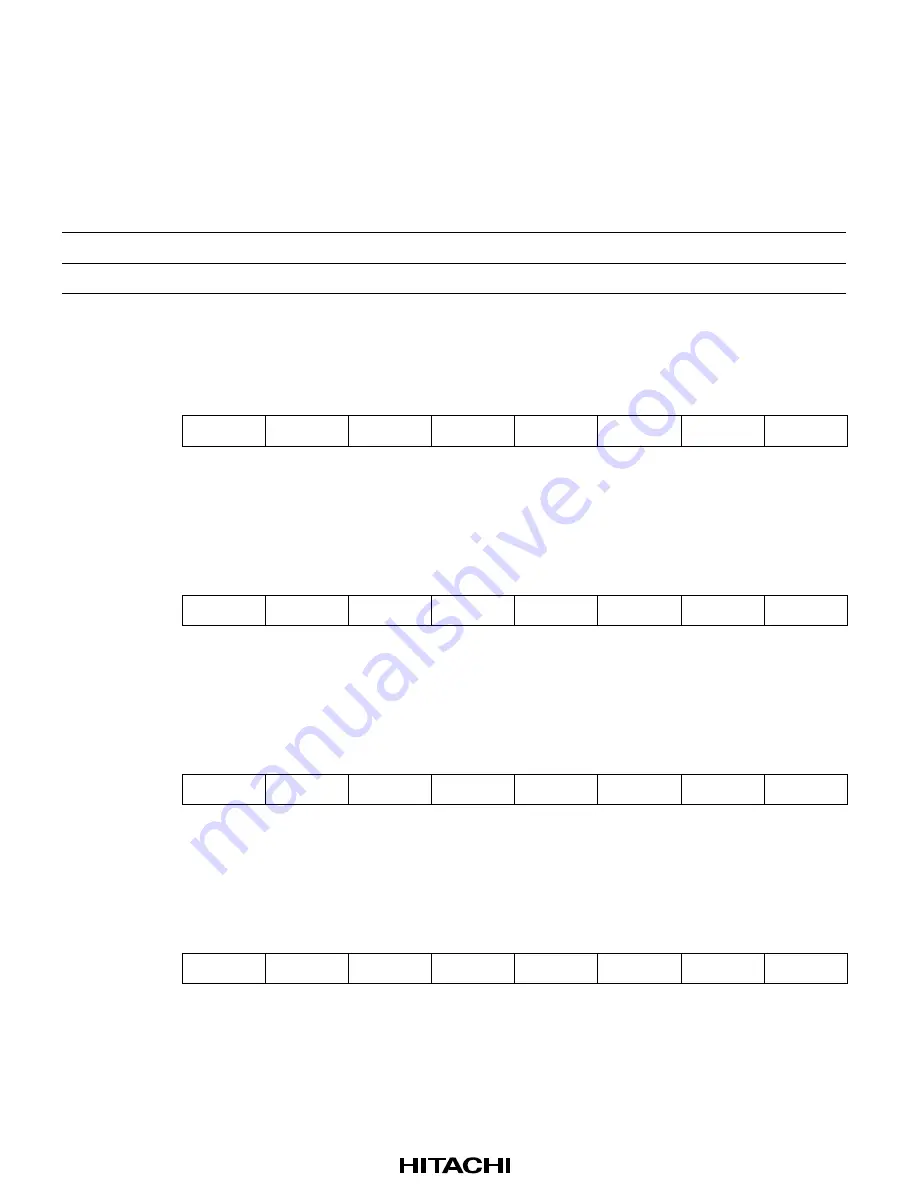

22.2.34

I/O Space Base Register (PCIIOBR)

Bit:

31

30

29

28

27

26

25

24

IOBR31

IOBR30

IOBR29

IOBR28

IOBR27

IOBR26

IOBR25

IOBR24

Initial value:

0

0

0

0

0

0

0

0

PCI-R/W:

—

—

—

—

—

—

—

—

PP Bus-R/W:

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

Bit:

23

22

21

20

19

18

17

16

IOBR23

IOBR22

IOBR21

IOBR20

IOBR19

IOBR18

—

—

Initial value:

0

0

0

0

0

0

0

0

PCI-R/W:

—

—

—

—

—

—

—

—

PP Bus-R/W:

R/W

R/W

R/W

R/W

R/W

R/W

R

R

Bit:

15

14

13

12

11

10

9

8

—

—

—

—

—

—

—

—

Initial value:

0

0

0

0

0

0

0

0

PCI-R/W:

—

—

—

—

—

—

—

—

PP Bus-R/W:

R

R

R

R

R

R

R

R

Bit:

7

6

5

4

3

2

1

0

—

—

—

—

—

—

—

LOCK

Initial value:

0

0

0

0

0

0

0

0

PCI-R/W:

—

—

—

—

—

—

—

—

PP Bus-R/W:

R

R

R

R

R

R

R

R/W

Summary of Contents for SH7751

Page 39: ...Rev 3 0 04 02 page xxxviii of xxxviii ...

Page 89: ...Rev 3 0 04 02 page 50 of 1064 ...

Page 157: ...Rev 3 0 04 02 page 118 of 1064 ...

Page 193: ...Rev 3 0 04 02 page 154 of 1064 ...

Page 225: ...Rev 3 0 04 02 page 186 of 1064 ...

Page 253: ...Rev 3 0 04 02 page 214 of 1064 ...

Page 301: ...Rev 3 0 04 02 page 262 of 1064 ...

Page 343: ...Rev 3 0 04 02 page 304 of 1064 ...

Page 607: ...Rev 3 0 04 02 page 568 of 1064 ...

Page 671: ...Rev 3 0 04 02 page 632 of 1064 ...

Page 745: ...Rev 3 0 04 02 page 706 of 1064 ...

Page 767: ...Rev 3 0 04 02 page 728 of 1064 ...

Page 1061: ...Rev 3 0 04 02 page 1022 of 1064 NMI tNMIL tNMIH Figure 23 69 NMI Input Timing ...

Page 1069: ...Rev 3 0 04 02 page 1030 of 1064 ...

Page 1103: ...Rev 3 0 04 02 page 1064 of 1064 ...