Rev. 3.0, 04/02, page 872 of 1064

22.2.37

PCI Clock Control Register (PCICLKR)

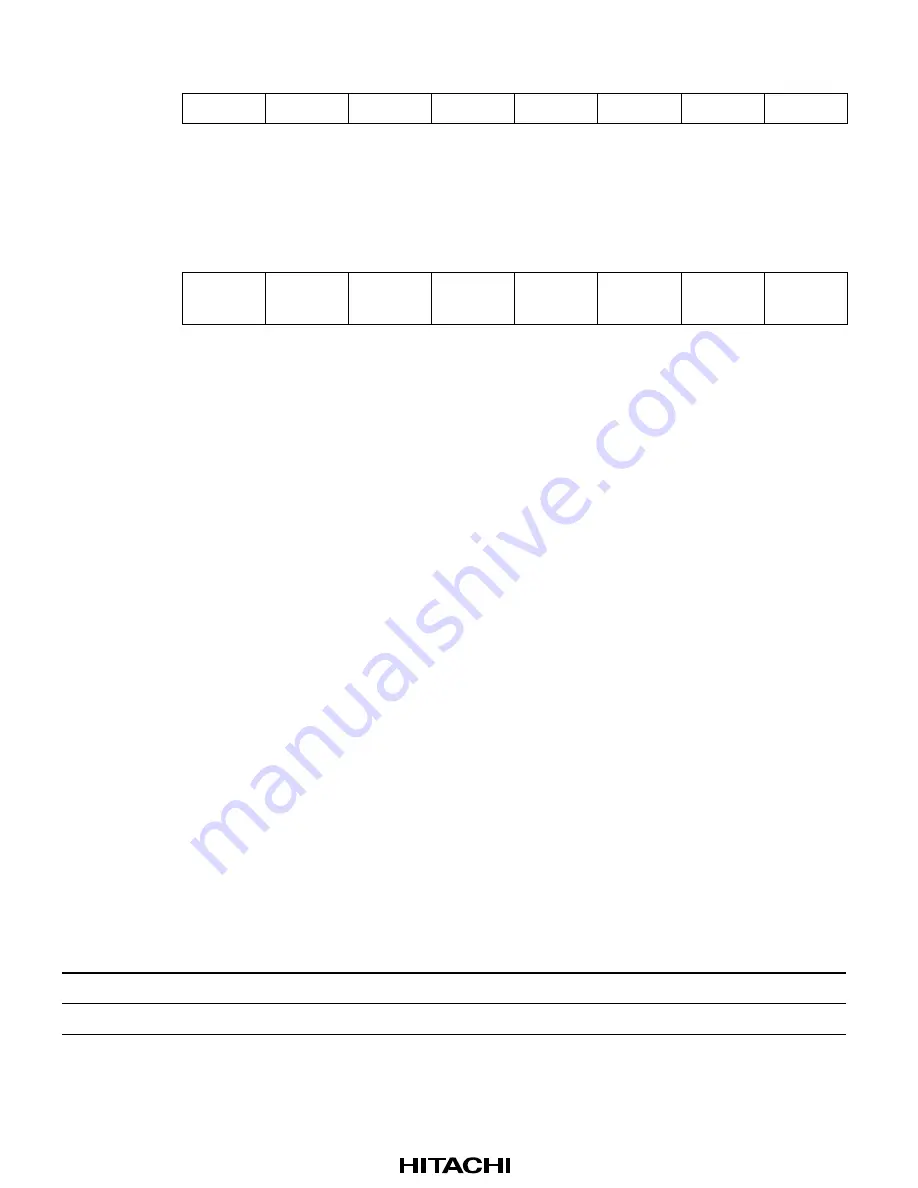

Bit:

31

30

29

. . .

11

10

9

8

—

—

—

. . .

—

—

—

—

Initial value:

0

0

0

. . .

0

0

0

0

PCI-R/W:

—

—

—

. . .

—

—

—

—

PP Bus-R/W:

R

R

R

. . .

R

R

R

R

Bit:

7

6

5

4

3

2

1

0

—

—

—

—

—

—

PCICLKS

TOP

BCLKST

OP

Initial value:

0

0

0

0

0

0

0

0

PCI-R/W:

—

—

—

—

—

—

—

—

PP Bus-R/W:

R

R

R

R

R

R

R/W

R/W

The PCI clock control register (PCICLKR) controls the stopping of the local bus clock (BCLK) in

the PCIC and the PCI bus clock. This 32-bit read/write register can be accessed from the PP bus.

The PCICLKR register is initialized to H'00000000 at a power-on reset. It is not initialized at a

software reset.

When the PCI bus clock is input from the external input pin

, the PCI bus clock can be

stopped by setting the PCICLKSTOP bit to 1. Likewise, the local bus clock can be stopped by

setting the BCLKSTOP bit to 1.

When the PCI bus clock is input via the CKIO pin, setting BCLKSTOP to 1 stops both the B

in

the PCIC and the feedback input clock from CKIO.

Writing to this register is valid only when bits 31 to 24 are H'A5.

Bits 31 to 2—Reserved: These bits are always read as 0. When writing, always write H'A5 to bits

31 to 24, and 0 to the other bits. Always write 0 to these bits when writing.

Bit 1—PCICLK Stop Control (PCICLKSTOP): Controls the stopping of the clock input via the

PCICLK pin.

Bit 1: PCICLKSTOP

Description

0

PCICLK input enabled

(Initial value)

1

Stop PCICLK input

Summary of Contents for SH7751

Page 39: ...Rev 3 0 04 02 page xxxviii of xxxviii ...

Page 89: ...Rev 3 0 04 02 page 50 of 1064 ...

Page 157: ...Rev 3 0 04 02 page 118 of 1064 ...

Page 193: ...Rev 3 0 04 02 page 154 of 1064 ...

Page 225: ...Rev 3 0 04 02 page 186 of 1064 ...

Page 253: ...Rev 3 0 04 02 page 214 of 1064 ...

Page 301: ...Rev 3 0 04 02 page 262 of 1064 ...

Page 343: ...Rev 3 0 04 02 page 304 of 1064 ...

Page 607: ...Rev 3 0 04 02 page 568 of 1064 ...

Page 671: ...Rev 3 0 04 02 page 632 of 1064 ...

Page 745: ...Rev 3 0 04 02 page 706 of 1064 ...

Page 767: ...Rev 3 0 04 02 page 728 of 1064 ...

Page 1061: ...Rev 3 0 04 02 page 1022 of 1064 NMI tNMIL tNMIH Figure 23 69 NMI Input Timing ...

Page 1069: ...Rev 3 0 04 02 page 1030 of 1064 ...

Page 1103: ...Rev 3 0 04 02 page 1064 of 1064 ...