Rev. 3.0, 04/02, page 874 of 1064

The PCI-BSC does not support mode register setting of synchronous DRAM nor refreshing of

synchronous DRAM or DRAM. These must be executed by the BSC.

Also, do not implement any settings that are not allowed in slave mode in the PCIC-BSC registers.

This is because bit 30: master/slave flag (MASTER) of the PCIBCR1 is fixed Low, regardless of

the value of the external master/slave setting pin (MP7) at a power-on reset, and the PCIC-BSC

therefore is set in slave mode.

In the case of external memory not used for data transfers with the PCI bus, make the same

settings as the corresponding bus state controller register.

These registers are initialized at a power-on reset, but not by a software reset.

Notes: *1 This register is provided only in the SH7751R, not provided in the SH7751.

*2 MPX is supported only in the SH7751R, not supported in the SH7751.

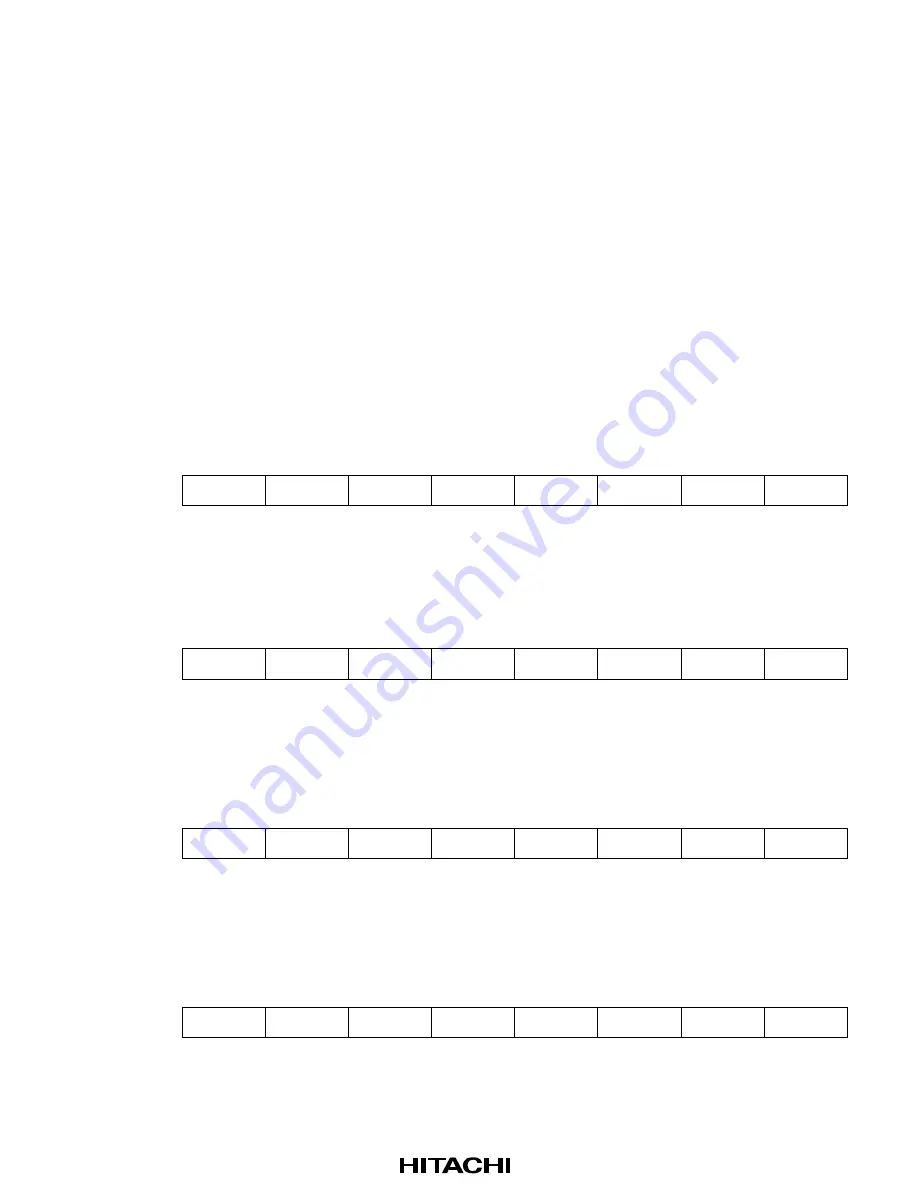

22.2.39

Port Control Register (PCIPCTR)

Bit:

31

30

29

28

27

26

25

24

—

—

—

—

—

—

—

—

Initial value:

0

0

0

0

0

0

0

0

PCI-R/W:

—

—

—

—

—

—

—

—

PP Bus-R/W:

R

R

R

R

R

R

R

R

Bit:

23

22

21

20

19

18

17

16

—

—

—

—

—

PORT2EN PORT1EN PORT0EN

Initial value:

0

0

0

0

0

0

0

0

PCI-R/W:

—

—

—

—

—

—

—

—

PP Bus-R/W:

R

R

R

R

R

R/W

R/W

R/W

Bit:

15

14

13

12

11

10

9

8

—

—

—

—

—

—

—

—

Initial value:

0

0

0

0

0

0

0

0

PCI-R/W:

—

—

—

—

—

—

—

—

PP Bus-R/W:

R

R

R

R

R

R

R

R

Bit:

7

6

5

4

3

2

1

0

—

—

PB2PUP

PB2IO

PB1PUP

PB1IO

PB0PUP

PB0IO

Initial value:

0

0

0

0

0

0

0

0

PCI-R/W:

—

—

—

—

—

—

—

—

PP Bus-R/W:

R

R

R/W

R/W

R/W

R/W

R/W

R/W

Summary of Contents for SH7751

Page 39: ...Rev 3 0 04 02 page xxxviii of xxxviii ...

Page 89: ...Rev 3 0 04 02 page 50 of 1064 ...

Page 157: ...Rev 3 0 04 02 page 118 of 1064 ...

Page 193: ...Rev 3 0 04 02 page 154 of 1064 ...

Page 225: ...Rev 3 0 04 02 page 186 of 1064 ...

Page 253: ...Rev 3 0 04 02 page 214 of 1064 ...

Page 301: ...Rev 3 0 04 02 page 262 of 1064 ...

Page 343: ...Rev 3 0 04 02 page 304 of 1064 ...

Page 607: ...Rev 3 0 04 02 page 568 of 1064 ...

Page 671: ...Rev 3 0 04 02 page 632 of 1064 ...

Page 745: ...Rev 3 0 04 02 page 706 of 1064 ...

Page 767: ...Rev 3 0 04 02 page 728 of 1064 ...

Page 1061: ...Rev 3 0 04 02 page 1022 of 1064 NMI tNMIL tNMIH Figure 23 69 NMI Input Timing ...

Page 1069: ...Rev 3 0 04 02 page 1030 of 1064 ...

Page 1103: ...Rev 3 0 04 02 page 1064 of 1064 ...