Rev. 3.0, 04/02, page 918 of 1064

0000

0001

0010

0011

0100

0100

0101

0110

0111

1000

1001

1010

1011

1100

1101

1110

1111

H’0 to H’F

PCI bus

B3 B2 B1 B0

31

0

BE

Configuration register

PCI bus

BE

Configuration register

B3 B2 B1 B0

31

0

B3 B2 B1

31

0

B3 B2

B0

31

0

B3 B2

31

0

B3

B1 B0

31

0

B3

B1 B0

31

0

B3

B1

31

0

B3

B0

31

0

B3

31

0

B2 B1 B0

31

0

B2 B1

31

0

B2

B0

31

0

B2

31

0

B1 B0

31

0

B1

31

0

B3 B2 B1 B0

31

0

31

0

H’0 to H’F

PCI bus

B3 B2 B1 B0

31

0

BE

Configuration register

B3 B2 B1 B0

31

0

B0

31

0

B3 B2 B1

31

0

B3 B2

B0

31

0

B3 B2

31

0

B3

B1 B0

31

0

B3

B1 B0

31

0

B3

B1

31

0

B3

B0

31

0

B3

31

0

B2 B1 B0

31

0

B2 B1

31

0

B2

B0

31

0

B2

31

0

B1 B0

31

0

B1

31

0

B3 B2 B1 B0

31

0

31

0

B0

31

0

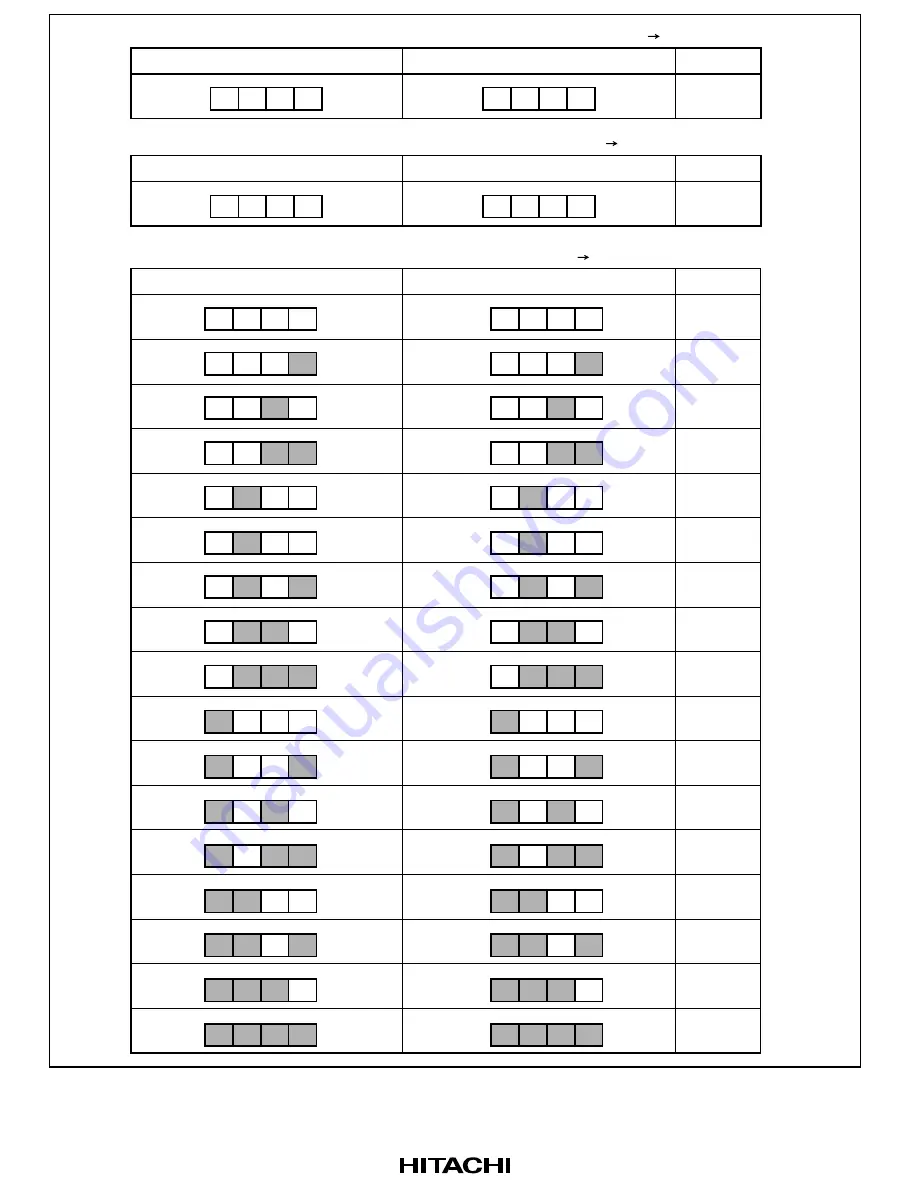

Target configuration read transfer data alignment (configuration register

PCI bus)

SH7751 target configuration write transfer data alignment (PCI bus

configuration register)

SH7751R target configuration transfer data alignment (PCI bus

configuration register)

Figure 22.23 Data Alignment at Target Configuration Transfer

(Both Big Endian and Little Endian)

Summary of Contents for SH7751

Page 39: ...Rev 3 0 04 02 page xxxviii of xxxviii ...

Page 89: ...Rev 3 0 04 02 page 50 of 1064 ...

Page 157: ...Rev 3 0 04 02 page 118 of 1064 ...

Page 193: ...Rev 3 0 04 02 page 154 of 1064 ...

Page 225: ...Rev 3 0 04 02 page 186 of 1064 ...

Page 253: ...Rev 3 0 04 02 page 214 of 1064 ...

Page 301: ...Rev 3 0 04 02 page 262 of 1064 ...

Page 343: ...Rev 3 0 04 02 page 304 of 1064 ...

Page 607: ...Rev 3 0 04 02 page 568 of 1064 ...

Page 671: ...Rev 3 0 04 02 page 632 of 1064 ...

Page 745: ...Rev 3 0 04 02 page 706 of 1064 ...

Page 767: ...Rev 3 0 04 02 page 728 of 1064 ...

Page 1061: ...Rev 3 0 04 02 page 1022 of 1064 NMI tNMIL tNMIH Figure 23 69 NMI Input Timing ...

Page 1069: ...Rev 3 0 04 02 page 1030 of 1064 ...

Page 1103: ...Rev 3 0 04 02 page 1064 of 1064 ...