Rev. 3.0, 04/02, page 920 of 1064

22.6

Interrupts

22.6.1

Interrupts from PCIC to CPU

There are 8 interrupts, as shown in the following, that can be generated by the PCIC for the CPU.

The interrupt controller also controls the individual interrupt priority levels and interrupt masks,

etc. See the section 19, Interrupt Controller (INTC), for details.

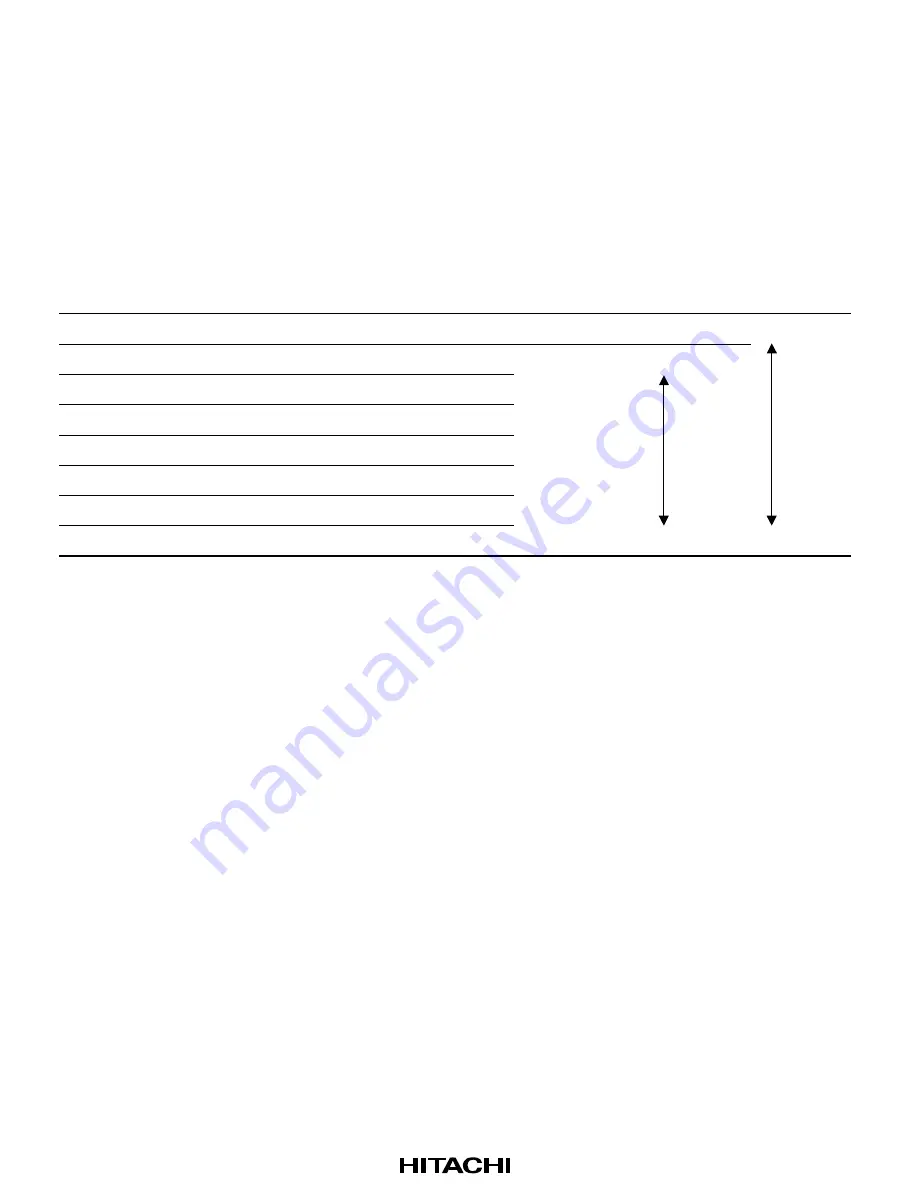

Table 22.13 Interrupts

Interrupt Source

Function

INTPRI00

Priority

PCISERR

SERR error interrupt

[3:0]

High

PCIERR

ERR error interrupt

[7:4]

High

PCIPWDWN

Power-down request interrupt

PCIPWON

Power-on request interrupt

PCIDMA0

DMA0 transfer end interrupt

PCIDMA1

DMA1 transfer end interrupt

PCIDMA2

DMA2 transfer end interrupt

PCIDMA3

DMA3 transfer end interrupt

Low

Low

System Error (

) Interrupt (PCISERR): This interrupt shows detection of the pin

being asserted. This interrupt is generated only when the PCIC is operating as host.

When the PCIC is operating as non-host, the SERR bit in the PCI control register (PCICR) is used

to notify the host device of the system error (assertion of

pin).

The

pin can be asserted when the SERR bit is asserted and when an address parity error is

detected in a target transfer.

When the SER bit of the PCI configuration register 1 (PCICONF1) is set to 0, the

pin is not

asserted.

Error Interrupt (PCIERR): Shows error detection by the PCIC. The error interrupt is asserted

when either of the following errors is detected:

Interrupts detected by PCI interrupt register (PCIINT)

Interrupts detected by PCI arbiter interrupt register (PCIAINT)

The interrupts that can be detected by these two registers can also be masked. The PCI interrupt

mask register (PCIINTM) masks the PCIINT interrupts, and the PCI arbiter interrupt mask register

(PCIAINTM) masks the PCIAINT interrupts. See section 22.2, PCIC Register Descriptions, for

details.

Summary of Contents for SH7751

Page 39: ...Rev 3 0 04 02 page xxxviii of xxxviii ...

Page 89: ...Rev 3 0 04 02 page 50 of 1064 ...

Page 157: ...Rev 3 0 04 02 page 118 of 1064 ...

Page 193: ...Rev 3 0 04 02 page 154 of 1064 ...

Page 225: ...Rev 3 0 04 02 page 186 of 1064 ...

Page 253: ...Rev 3 0 04 02 page 214 of 1064 ...

Page 301: ...Rev 3 0 04 02 page 262 of 1064 ...

Page 343: ...Rev 3 0 04 02 page 304 of 1064 ...

Page 607: ...Rev 3 0 04 02 page 568 of 1064 ...

Page 671: ...Rev 3 0 04 02 page 632 of 1064 ...

Page 745: ...Rev 3 0 04 02 page 706 of 1064 ...

Page 767: ...Rev 3 0 04 02 page 728 of 1064 ...

Page 1061: ...Rev 3 0 04 02 page 1022 of 1064 NMI tNMIL tNMIH Figure 23 69 NMI Input Timing ...

Page 1069: ...Rev 3 0 04 02 page 1030 of 1064 ...

Page 1103: ...Rev 3 0 04 02 page 1064 of 1064 ...