Rev. 3.0, 04/02, page 958 of 1064

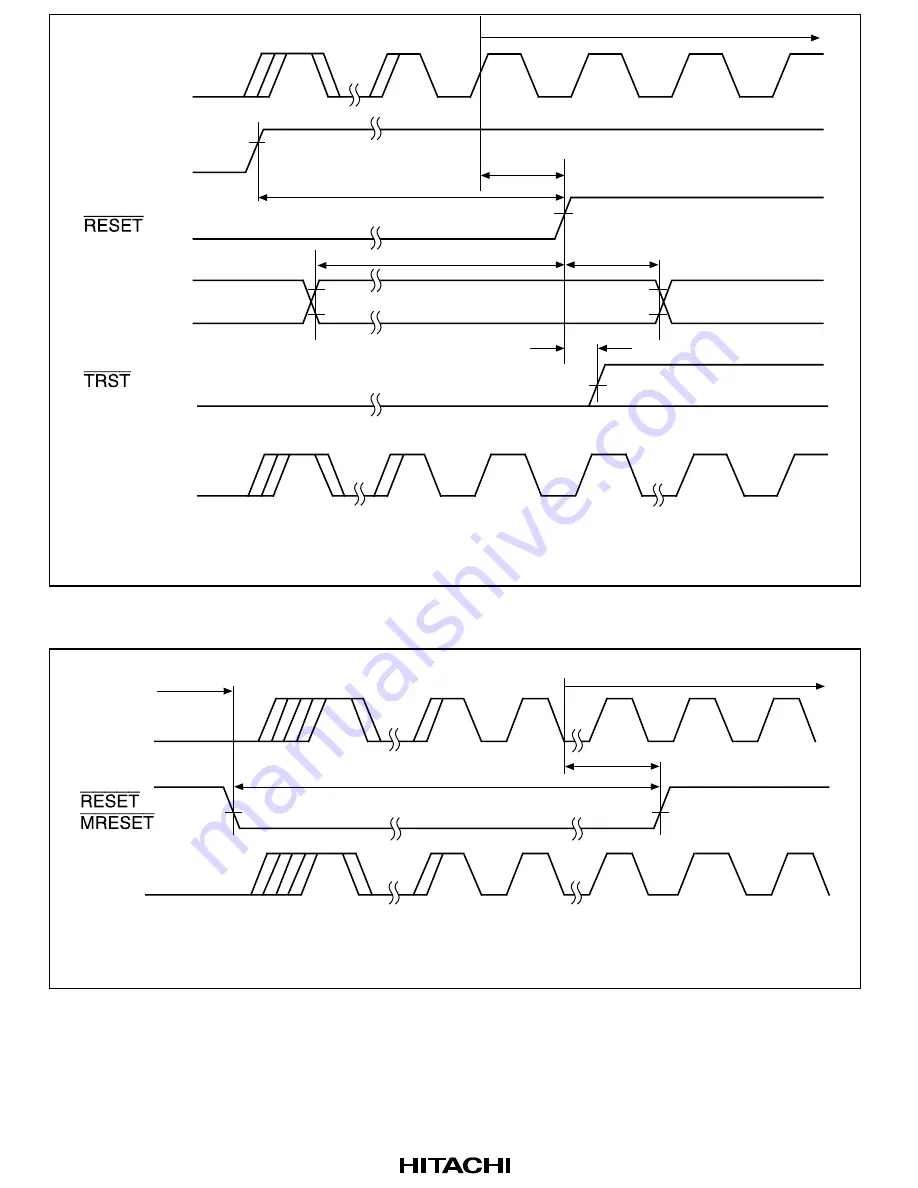

Internal clock

VDD

MD10 to MD0

t

OSC1

V

DD

min

t

MDRH

t

OSCMD

t

TRSTRH

Stable oscillation

t

RESW

CKIO

Notes: 1. Oscillation settling time when on-chip resonator is used

2. PLL2 operating

Figure 23.5 Power-On Oscillation Settling Time

or

t

RESW

t

OSC2

CKIO

Stable oscillation

Standby

Internal

clock

Notes: 1. Oscillation settling time when on-chip resonator is used

2. PLL2 operating

Figure 23.6 Standby Return Oscillation Settling Time (Return by

or

)

Summary of Contents for SH7751

Page 39: ...Rev 3 0 04 02 page xxxviii of xxxviii ...

Page 89: ...Rev 3 0 04 02 page 50 of 1064 ...

Page 157: ...Rev 3 0 04 02 page 118 of 1064 ...

Page 193: ...Rev 3 0 04 02 page 154 of 1064 ...

Page 225: ...Rev 3 0 04 02 page 186 of 1064 ...

Page 253: ...Rev 3 0 04 02 page 214 of 1064 ...

Page 301: ...Rev 3 0 04 02 page 262 of 1064 ...

Page 343: ...Rev 3 0 04 02 page 304 of 1064 ...

Page 607: ...Rev 3 0 04 02 page 568 of 1064 ...

Page 671: ...Rev 3 0 04 02 page 632 of 1064 ...

Page 745: ...Rev 3 0 04 02 page 706 of 1064 ...

Page 767: ...Rev 3 0 04 02 page 728 of 1064 ...

Page 1061: ...Rev 3 0 04 02 page 1022 of 1064 NMI tNMIL tNMIH Figure 23 69 NMI Input Timing ...

Page 1069: ...Rev 3 0 04 02 page 1030 of 1064 ...

Page 1103: ...Rev 3 0 04 02 page 1064 of 1064 ...