Rev. 1.60

202

August 20, 2019

Rev. 1.60

203

August 20, 2019

BS66F340/BS66F350/BS66F360/BS66F370

Touch A/D Flash MCU with LED Driver

BS66F340/BS66F350/BS66F360/BS66F370

Touch A/D Flash MCU with LED Driver

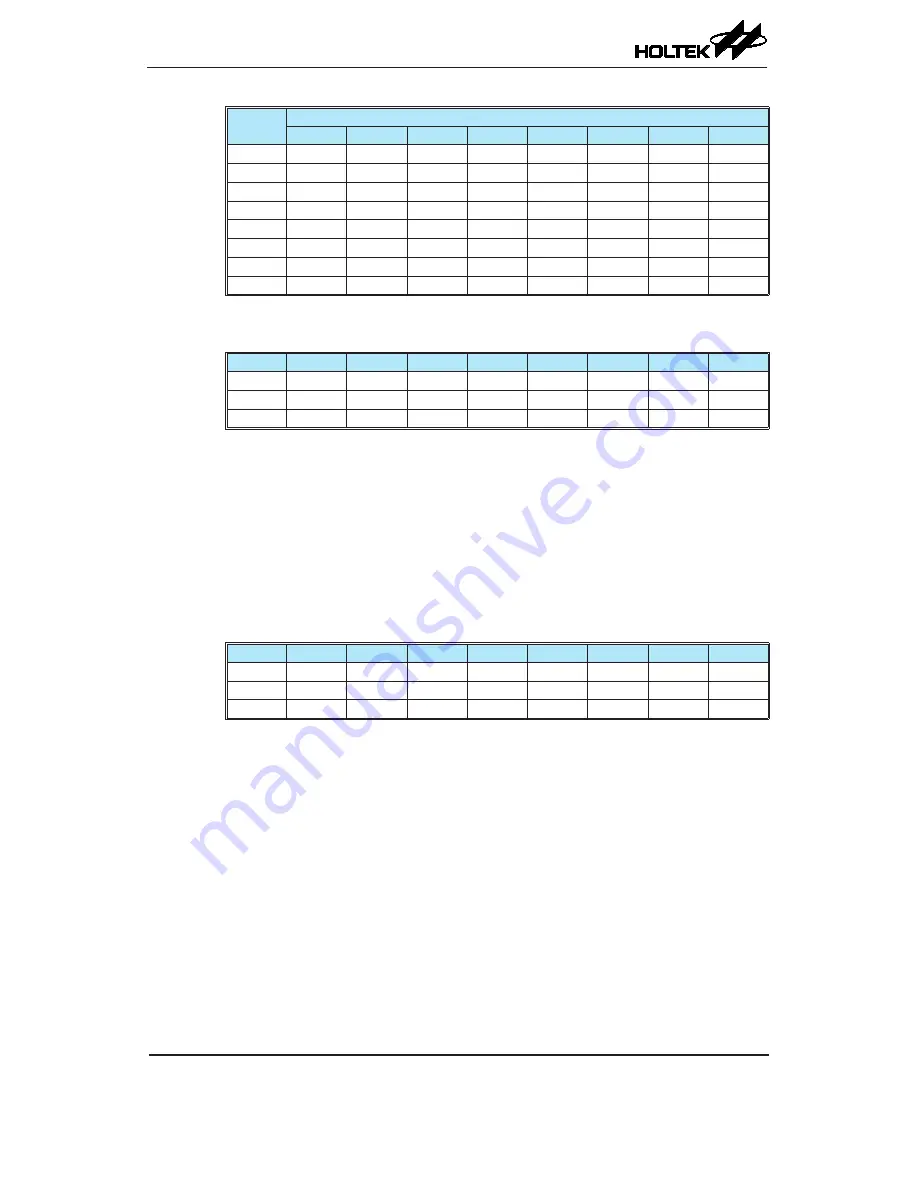

Register

Name

Bit

7

6

5

4

3

2

1

0

INTEG

—

—

—

—

INT1S1

INT1S0

INT0S1

INT0S0

INTC0

—

TKMF

INT1F

INT0F

TKME

INT1E

INT0E

EMI

INTC1

ADF

MF1F

MF0F

URF

ADE

MF1E

MF0E

URE

INTC2

MF3F

TB1F

TB0F

MF2F

MF3E

TB1E

TB0E

MF2E

MFI0

—

—

CTM0AF CTM0PF

—

—

CTM0AE CTM0PE

MFI1

STMAF

STMPF CTM1AF CTM1PF STMAE

STMPE CTM1AE CTM1PE

MFI2

—

SIMF

PTMAF

PTMPF

—

SIME

PTMAE

PTMPE

MFI3

—

—

DEF

LVF

—

—

DEE

LVE

Interrupt Registers List

• INTEG Register

Bit

7

6

5

4

3

2

1

0

Name

—

—

—

—

INT1S1

INT1S0

INT0S1

INT0S0

R/W

—

—

—

—

R/W

R/W

R/W

R/W

POR

—

—

—

—

0

0

0

0

Bit 7~4

Unimplemented, read as "0"

Bit 3~2

INT1S1~INT1S0

: Interrupt edge control for INT1 pin

00: Disable

01: Rising edge

10: Falling edge

11: Rising and falling edges

Bit 1~0

INT0S1~INT0S0

: Interrupt edge control for INT0 pin

00: Disable

01: Rising edge

10: Falling edge

11: Rising and falling edges

• INTC0 Register

Bit

7

6

5

4

3

2

1

0

Name

—

TKMF

INT1F

INT0F

TKME

INT1E

INT0E

EMI

R/W

—

R/W

R/W

R/W

R/W

R/W

R/W

R/W

POR

—

0

0

0

0

0

0

0

Bit 7

Unimplemented, read as "0"

Bit 6

TKMF

: Touch key interrupt request flag

0: No request

1: Interrupt request

Bit 5

INT1F

: INT1 interrupt request flag

0: No request

1: Interrupt request

Bit 4

INT0F

: INT0 interrupt request flag

0: No request

1: Interrupt request

Bit 3

TKME

: Touch key interrupt control

0: Disable

1: Enable

Bit 2

INT1E

: INT1 interrupt control

0: Disable

1: Enable

Bit 1

INT0E

: INT0 interrupt control

0: Disable

1: Enable