Rev. 1.50

13�

����st ��� �01�

Rev. 1.50

133

����st ��� �01�

HT66F0175/HT66F0185

A/D Flash MCU with EEPROM

HT66F0175/HT66F0185

A/D Flash MCU with EEPROM

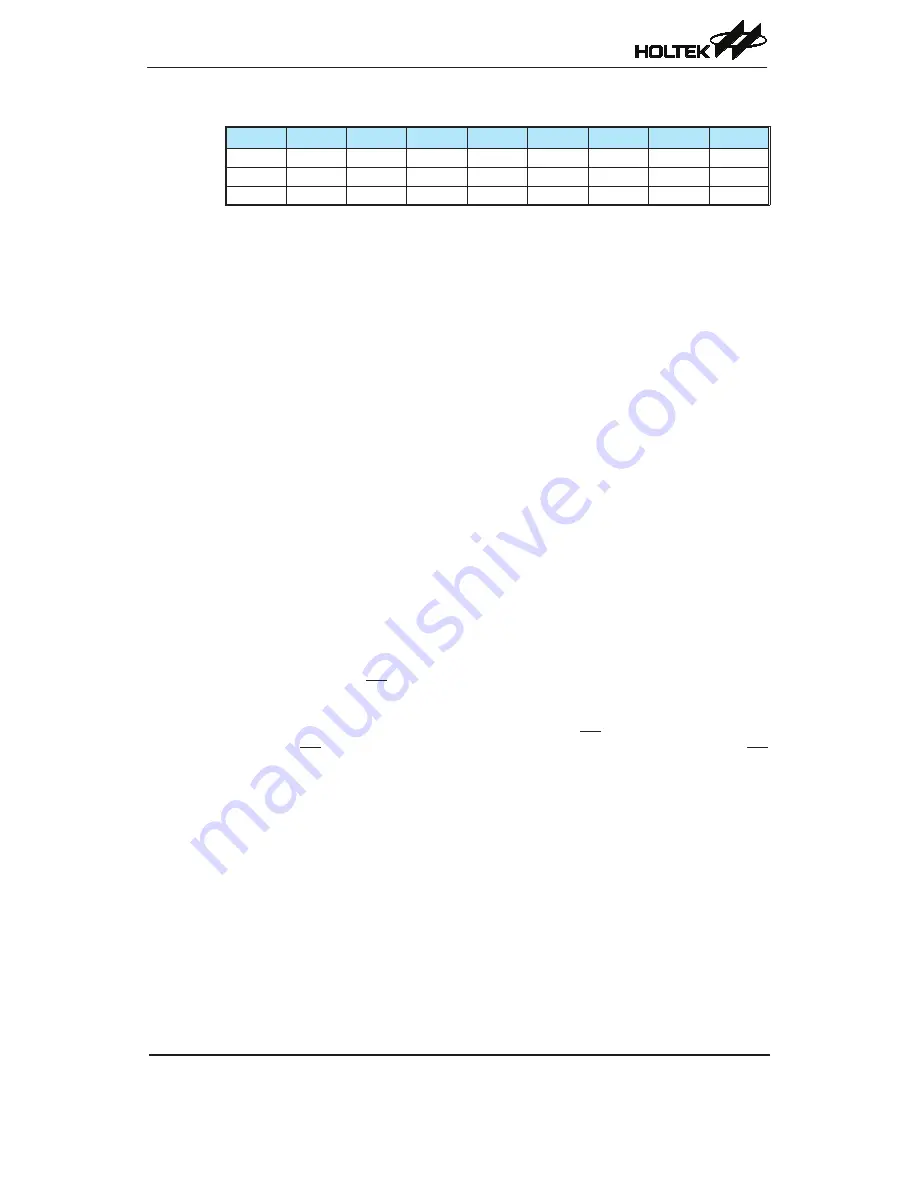

SIMC2 Register

Bit

7

6

5

4

3

2

1

0

Name

D�

D6

CKPOLB

CKEG

MLS

CSEN

WCOL

TRF

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

POR

0

0

0

0

0

0

0

0

Bit 7~6

Undefined bits

These bits can be read or written by the application program.

Bit 5

CKPOLB

: SPI clock line base condition selection

0: The SCK line will be high when the clock is inactive.

1: The SCK line will be low when the clock is inactive.

The CKPOLB bit determines the base condition of the clock line, if the bit is high,

then the SCK line will be low when the clock is inactive. When the CKPOLB bit is

low, then the SCK line will be high when the clock is inactive.

Bit 4

CKEG

: SPI SCK clock active edge type selection

CKPOLB=0

0: SCK is high base level and data capture at SCK rising edge

1: SCK is high base level and data capture at SCK falling edge

CKPOLB=1

0: SCK is low base level and data capture at SCK falling edge

1: SCK is low base level and data capture at SCK rising edge

The CKEG and CKPOLB bits are used to setup the way that the clock signal outputs

and inputs data on the SPI bus. These two bits must be configured before data transfer

is executed otherwise an erroneous clock edge may be generated. The CKPOLB bit

determines the base condition of the clock line, if the bit is high, then the SCK line

will be low when the clock is inactive. When the CKPOLB bit is low, then the SCK

line will be high when the clock is inactive. The CKEG bit determines active clock

edge type which depends upon the condition of CKPOLB bit.

Bit 3

MLS

: SPI data shift order

0: LSB first

1: MSB first

This is the data shift select bit and is used to select how the data is transferred, either

MSB or LSB first. Setting the bit high will select MSB first and low for LSB first.

Bit 2

CSEN

: SPI SCS pin control

0: Disable

1: Enable

The CSEN bit is used as an enable/disable for the SCS pin. If this bit is low, then the

SCS pin will be disabled and placed into a floating condition. If the bit is high, the SCS

pin will be enabled and used as a select pin.

Bit 1

WCOL

: SPI write collision flag

0: No collision

1: Collision

The WCOL flag is used to detect whether a data collision has occurred or not. If this

bit is high, it means that data has been attempted to be written to the SIMD register

duting a data transfer operation. This writing operation will be ignored if data is being

transferred. This bit can be cleared by the application program.

Bit 0

TRF

: SPI Transmit/Receive complete flag

0: SPI data is being transferred

1: SPI data transfer is completed

The TRF bit is the Transmit/Receive Complete flag and is set to 1 automatically when

an SPI data transfer is completed, but must cleared to 0 by the application program. It

can be used to generate an interrupt.