Rev. 1.50

16

����st ��� �01�

Rev. 1.50

1�

����st ��� �01�

HT66F0175/HT66F0185

A/D Flash MCU with EEPROM

HT66F0175/HT66F0185

A/D Flash MCU with EEPROM

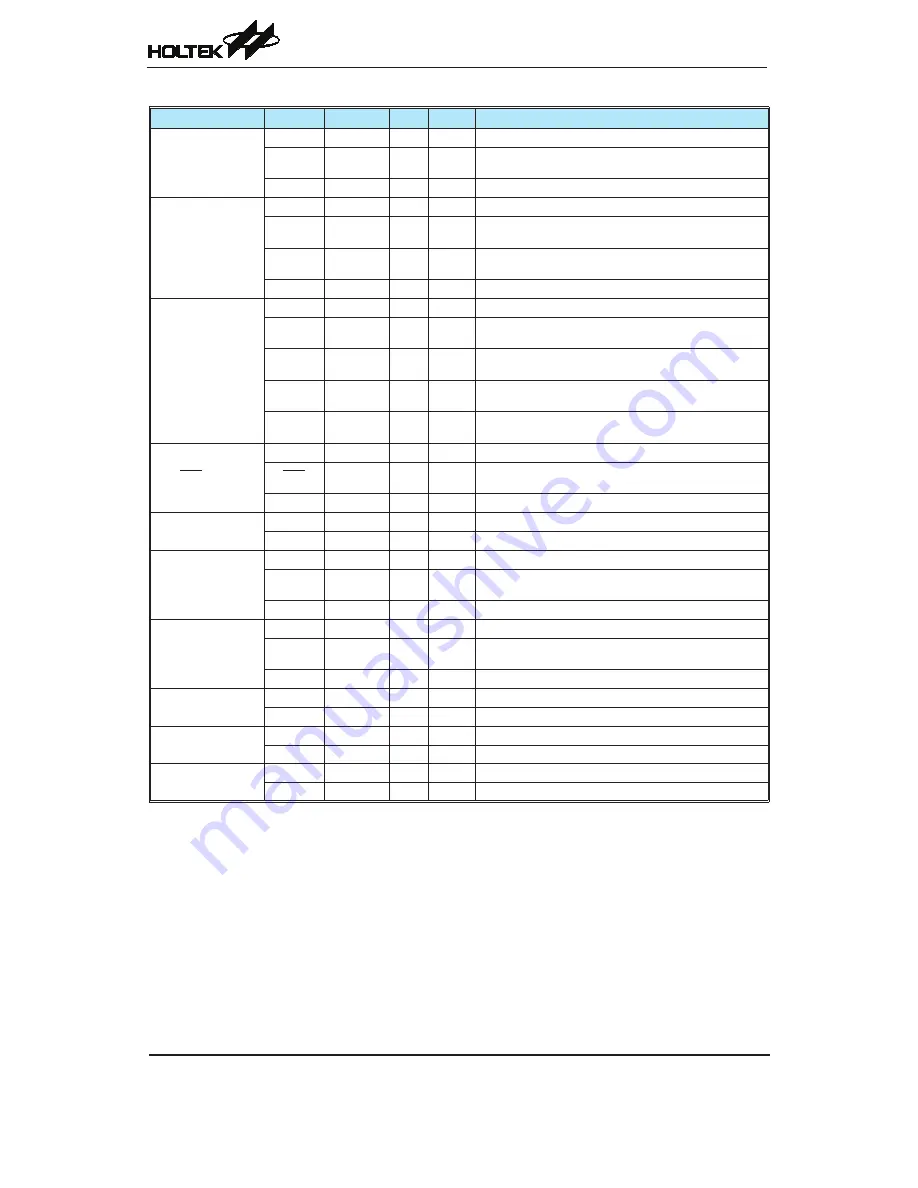

Pad Name

Function

OPT

I/T

O/T

Description

PC3/SDO/SSEG�1

PC3

PCPU

ST

CMOS General p�rpose I/O. Re�ister enabled p�ll-�p.

SDO

SIMC0

IFS

—

CMOS SPI data o�tp�t

SSEG�1 SLCDC3

—

SSEG Software controlled LCD se�ment o�tp�t

PC4/SDI/SD�//

SSEG��

PC4

PCPU

ST

CMOS General p�rpose I/O. Re�ister enabled p�ll-�p.

SDI

SIMC0

IFS

ST

—

SPI data inp�t

SD�

SIMC0

IFS

ST

NMOS I

�

C data line

SSEG�� SLCDC4

—

SSEG Software controlled LCD se�ment o�tp�t

PC5/SCK/SCL/

SSEG1/SCOM1

PC5

PCPU

ST

CMOS General p�rpose I/O. Re�ister enabled p�ll-�p.

SCK

SIMC0

IFS

ST

CMOS SPI serial clock

SCL

SIMC0

IFS

ST

NMOS I

�

C clock line

SSEG1

SLCDC0

SLCDC1

—

SSEG Software controlled LCD se�ment o�tp�t

SCOM1

SLCDC0

SLCDC1

—

SCOM Software controlled LCD common o�tp�t

PC6/SCS/SSEG�3

PC6

PCPU

ST

CMOS General p�rpose I/O. Re�ister enabled p�ll-�p.

SCS

SLCDC0

SIMC0 IFS ST

CMOS SPI slave select

SSEG�3 SLCDC4

—

SSEG Software controlled LCD se�ment o�tp�t

PD0/SSEG11

PD0

PDPU

ST

CMOS General p�rpose I/O. Re�ister enabled p�ll-�p.

SSEG11 SLCDC�

—

SSEG Software controlled LCD se�ment o�tp�t

PD1/RX/SSEG1�

PD1

PDPU

ST

CMOS General p�rpose I/O. Re�ister enabled p�ll-�p.

RX

UCR1

UCR�

ST

—

U�RT RX serial data inp�t

SSEG1� SLCDC�

—

SSEG Software controlled LCD se�ment o�tp�t

PD�/TX/SSEG13

PD�

PDPU

ST

CMOS General p�rpose I/O. Re�ister enabled p�ll-�p.

TX

UCR1

UCR�

—

CMOS U�RT TX serial data o�tp�t

SSEG13 SLCDC�

—

SSEG Software controlled LCD se�ment o�tp�t

PD3/SSEG14

PD3

PDPU

ST

CMOS General p�rpose I/O. Re�ister enabled p�ll-�p.

SSEG14 SLCDC3

—

SSEG Software controlled LCD se�ment o�tp�t

VDD&�VDD

VDD

—

PWR

—

Positive power s�pply

�VDD

—

PWR

—

�/D converter positive power s�pply

VSS&�VSS

VSS

—

PWR

—

Ne�ative power s�pply� �ro�nd.

�VSS

—

PWR

—

�/D converter ne�ative power s�pply� �ro�nd.

Note: I/T: Input type;

O/T: Output type;

OPT: Optional by configuration option (CO) or register option;

CO: Configuration option;

ST: Schmitt Trigger input; AN: Analog input;

CMOS: CMOS output;

NMOS: NMOS output;

AO: Analog output;

SSEG: Software controlled LCD SEG;

SCOM: Software controlled LCD COM;

HXT: High frequency crystal oscillator;

LXT: Low frequency crystal oscillator

PWR: Power

* The AVDD pin is internally bonded together with the VDD pin while the AVSS pin is internally bonded

together with the VSS pin.

As the Pin Description Summary table applies to the package type with the most pins, not all of the above listed

pins may be present on package types with smaller numbers of pins.