Rev. 1.50

��

����st ��� �01�

Rev. 1.50

�9

����st ��� �01�

HT66F0175/HT66F0185

A/D Flash MCU with EEPROM

HT66F0175/HT66F0185

A/D Flash MCU with EEPROM

Look-up Table

Any location within the Program Memory can be defined as a look-up table where programmers can

store fixed data. To use the look-up table, the table pointer must first be setup by placing the address

of the look up data to be retrieved in the table pointer register, TBLP and TBHP. These registers

define the total address of the look-up table.

After setting up the table pointer, the table data can be retrieved from the Program Memory using

the “TABRD [m]” or “TABRDL [m]” instructions respectively. When the instruction is executed,

the lower order table byte from the Program Memory will be transferred to the user defined

Data Memory register [m] as specified in the instruction. The higher order table data byte from

the Program Memory will be transferred to the TBLH special register. Any unused bits in this

transferred higher order byte will be read as “0”.

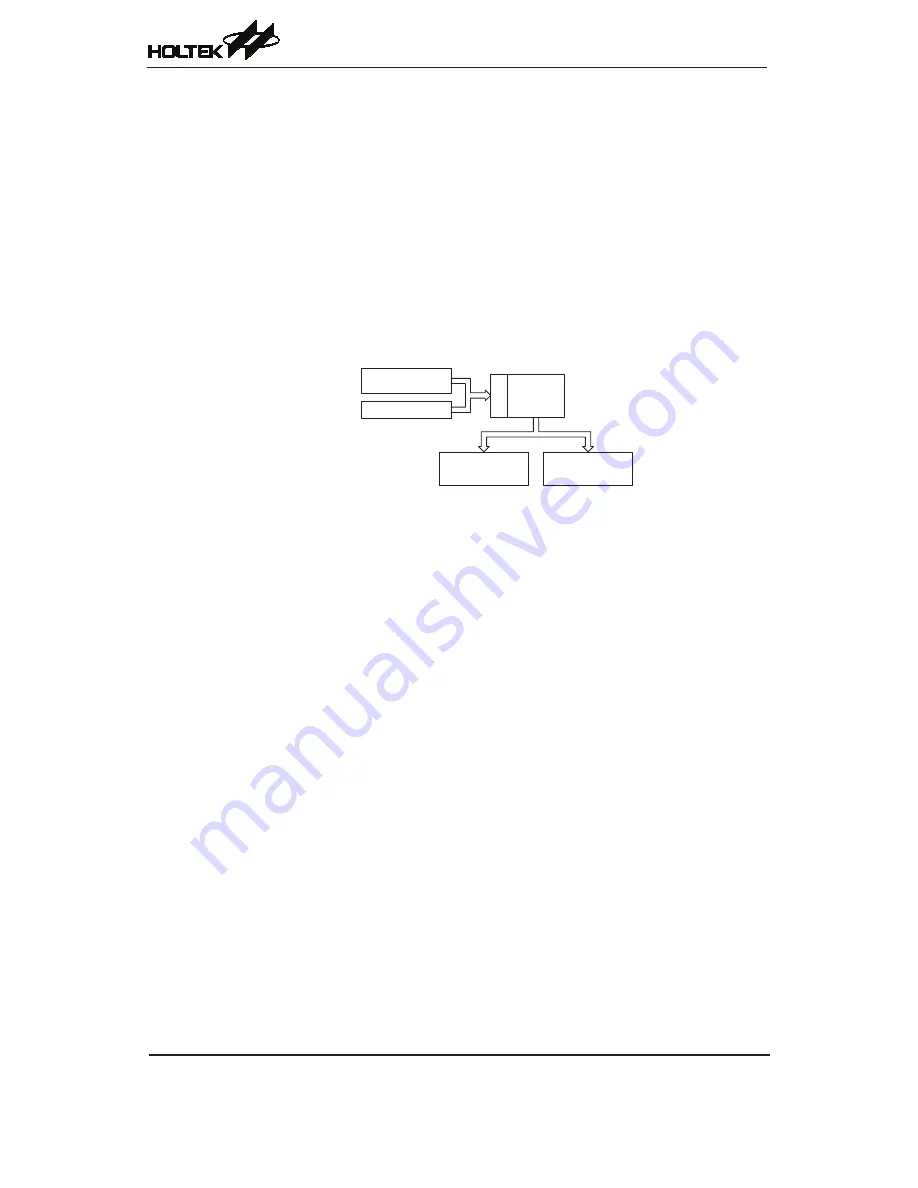

The accompanying diagram illustrates the addressing data flow of the look-up table.

R e g i s t e r T B L H

U s e r S e l e c t e d

R e g i s t e r

H i g h B y t e

L o w B y t e

T B L P R e g i s t e r

D a t a

Addr

es

s

1 6 b i t s

L a s t p a g e o r

T B H P R e g i s t e r

Table Program Example

The accompanying example shows how the table pointer and table data is defined and retrieved from

the device. This example uses raw table data located in the last page which is stored there using the

ORG statement. The value at this ORG statement is “0F00H” which refers to the start address of the

last page within the 4K Program Memory of the device. The table pointer low byte register is setup

here to have an initial value of “06H”. This will ensure that the first data read from the data table

will be at the Program Memory address “0F06H” or 6 locations after the start of the last page. Note

that the value for the table pointer is referenced to the first address of the present page pointed by the

TBHP register if the “TABRD [m]” instruction is being used. The high byte of the table data which

in this case is equal to zero will be transferred to the TBLH register automatically when the “TABRD

[m] instruction is executed.

Because the TBLH register is a read-only register and cannot be restored, care should be taken

to ensure its protection if both the main routine and Interrupt Service Routine use table read

instructions. If using the table read instructions, the Interrupt Service Routines may change the

value of the TBLH and subsequently cause errors if used again by the main routine. As a rule it is

recommended that simultaneous use of the table read instructions should be avoided. However, in

situations where simultaneous use cannot be avoided, the interrupts should be disabled prior to the

execution of any main routine table-read instructions. Note that all table related instructions require

two instruction cycles to complete their operation.