Rev. 1.50

6�

����st ��� �01�

Rev. 1.50

63

����st ��� �01�

HT66F0175/HT66F0185

A/D Flash MCU with EEPROM

HT66F0175/HT66F0185

A/D Flash MCU with EEPROM

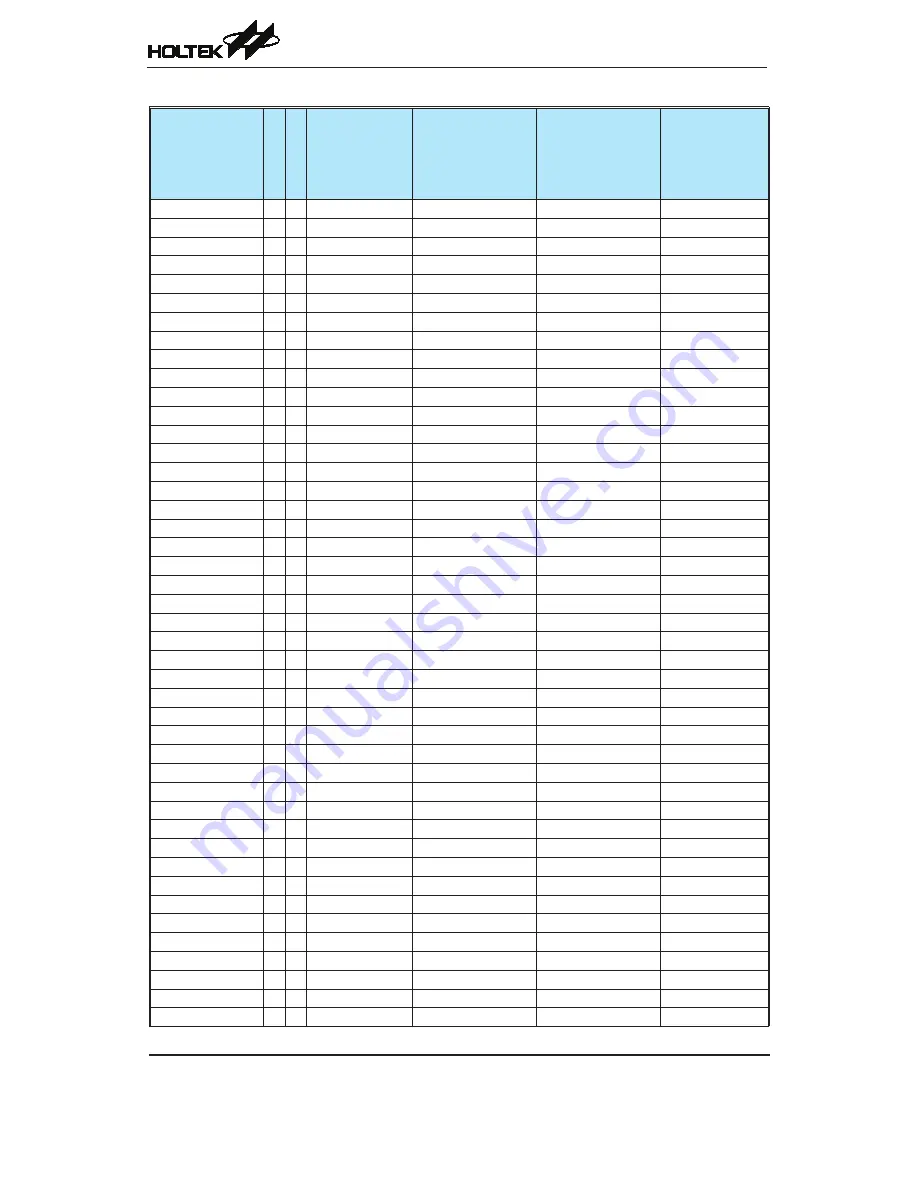

Register

HT66F0175

HT66F0185

Reset

(Power On)

LVR Reset

(Normal Operation)

WDT Time-out

(Normal Operation)

WDT Time-out

(IDLE or SLEEP)*

PBPU

● ●

- 0 0 0 0 0 0 0

- 0 0 0 0 0 0 0

- 0 0 0 0 0 0 0

- � � � � � � �

TM�C0

●

0 0 0 0 0 - - -

0 0 0 0 0 - - -

0 0 0 0 0 - - -

� � � � � - - -

TM�C1

●

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

� � � � � � � �

TM�DL

●

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

� � � � � � � �

TM�DH

●

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

� � � � � � � �

TM��L

●

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

� � � � � � � �

TM��H

●

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

� � � � � � � �

TM�RP

●

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

� � � � � � � �

TM0C0

●

0 0 0 0 0 - - -

0 0 0 0 0 - - -

0 0 0 0 0 - - -

� � � � � - - -

TM0C1

●

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

� � � � � � � �

TM0DL

●

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

� � � � � � � �

TM0DH

●

- - - - - - - 0 0

- - - - - - 0 0

- - - - - - 0 0

- - - - - - � �

TM0�L

●

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

� � � � � � � �

TM0�H

●

- - - - - - - 0 0

- - - - - - 0 0

- - - - - - 0 0

- - - - - - � �

TM0RPL

●

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

� � � � � � � �

TM0RPH

●

- - - - - - - 0 0

- - - - - - 0 0

- - - - - - 0 0

- - - - - - � �

TM0C0

●

0 0 0 0 0 - - -

0 0 0 0 0 - - -

0 0 0 0 0 - - -

� � � � � - - -

TM0C1

●

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

� � � � � � � �

TM0DL

●

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

� � � � � � � �

TM0DH

●

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

� � � � � � � �

TM0�L

●

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

� � � � � � � �

TM0�H

●

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

� � � � � � � �

TM0RP

●

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

� � � � � � � �

TM1C0

● ●

0 0 0 0 0 - - -

0 0 0 0 0 - - -

0 0 0 0 0 - - -

� � � � � - - -

TM1C1

● ●

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

� � � � � � � �

TM1DL

● ●

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

� � � � � � � �

TM1DH

● ●

- - - - - - - 0 0

- - - - - - 0 0

- - - - - - 0 0

- - - - - - � �

TM1�L

● ●

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

� � � � � � � �

TM1�H

● ●

- - - - - - - 0 0

- - - - - - 0 0

- - - - - - 0 0

- - - - - - � �

TM1RPL

● ●

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

� � � � � � � �

TM1RPH

● ●

- - - - - - - 0 0

- - - - - - 0 0

- - - - - - 0 0

- - - - - - � �

CPC

●

1 0 0 0 0 0 0 1

1 0 0 0 0 0 0 1

1 0 0 0 0 0 0 1

� � � � � � � �

PC

● ●

- 1 1 1 1 1 1 1

- 1 1 1 1 1 1 1

- 1 1 1 1 1 1 1

- � � � � � � �

PCC

● ●

- 1 1 1 1 1 1 1

- 1 1 1 1 1 1 1

- 1 1 1 1 1 1 1

- � � � � � � �

PCPU

● ●

- 0 0 0 0 0 0 0

- 0 0 0 0 0 0 0

- 0 0 0 0 0 0 0

- � � � � � � �

�CERL

● ●

1 1 1 1 1 1 1 1

1 1 1 1 1 1 1 1

1 1 1 1 1 1 1 1

� � � � � � � �

SIMC0

● ●

111 - 0 0 0 0

111 - 0 0 0 0

111 - 0 0 0 0

� � � - � � � �

SIMC1

● ●

1 0 0 0 0 0 0 1

1 0 0 0 0 0 0 1

1 0 0 0 0 0 0 1

� � � � � � � �

SIMD

● ●

x x x x x x x x

x x x x x x x x

x x x x x x x x

� � � � � � � �

SIM�/SIMC�

● ●

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

� � � � � � � �

SIMTOC

● ●

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

� � � � � � � �

SLCDC0

● ●

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

� � � � � � � �

SLCDC1

● ●

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

� � � � � � � �

SLCDC�

● ●

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

� � � � � � � �