Rev. 1.50

94

����st ��� �01�

Rev. 1.50

95

����st ��� �01�

HT66F0175/HT66F0185

A/D Flash MCU with EEPROM

HT66F0175/HT66F0185

A/D Flash MCU with EEPROM

Timer/Counter Mode

To select this mode, bits TnM1 and TnM0 in the TMnC1 register should be set to 11 respectively.

The Timer/Counter Mode operates in an identical way to the Compare Match Output Mode

generating the same interrupt flags. The exception is that in the Timer/Counter Mode the TMn output

pin is not used. Therefore the above description and Timing Diagrams for the Compare Match

Output Mode can be used to understand its function. As the TMn output pin is not used in this mode,

the pin can be used as a normal I/O pin or other pin-shared function.

PWM Output Mode

To select this mode, bits TnM1 and TnM0 in the TMnC1 register should be set to 10 respectively

and also the TnIO1 and TnIO0 bits should be set to 10 respectively. The PWM function within

the TMn is useful for applications which require functions such as motor control, heating control,

illumination control etc. By providing a signal of fixed frequency but of varying duty cycle on the

TMn output pin, a square wave AC waveform can be generated with varying equivalent DC RMS

values.

As both the period and duty cycle of the PWM waveform can be controlled, the choice of generated

waveform is extremely flexible. In the PWM mode, the TnCCLR bit has no effect as the PWM

period. Both of the CCRA and CCRP registers are used to generate the PWM waveform, one register

is used to clear the internal counter and thus control the PWM waveform frequency, while the other

one is used to control the duty cycle. Which register is used to control either frequency or duty cycle

is determined using the TnDPX bit in the TMnC1 register. The PWM waveform frequency and duty

cycle can therefore be controlled by the values in the CCRA and CCRP registers.

An interrupt flag, one for each of the CCRA and CCRP, will be generated when a compare match

occurs from either Comparator A or Comparator P. The TnOC bit in the TMnC1 register is used to

select the required polarity of the PWM waveform while the two TnIO1 and TnIO0 bits are used to

enable the PWM output or to force the TMn output pin to a fixed high or low level. The TnPOL bit

is used to reverse the polarity of the PWM output waveform.

•

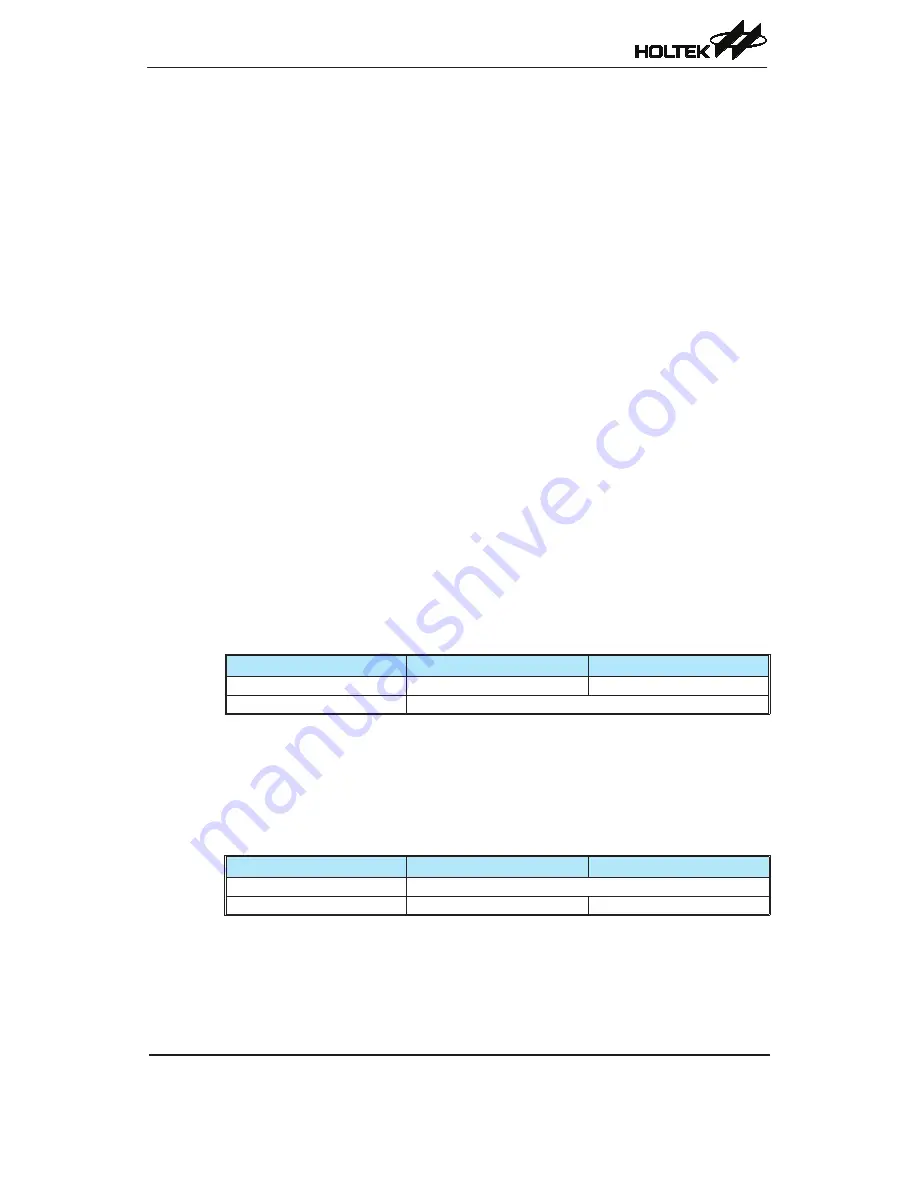

16-bit STM, PWM Mode, Edge-aligned Mode, TnDPX=0

CCRP

1~255

0

Period

CCRP

×

�56

65536

D�ty

CCR�

If f

SYS

= 16MHz, TMn clock source is f

SYS

/4, CCRP = 2 and CCRA = 128,

The TMn PWM output frequency = (f

SYS

/4) / (2×256) = f

SYS

/2048 = 7.8125 kHz, duty = 128/(2×256)=

25%.

If the Duty value defined by the CCRA register is equal to or greater than the Period value, then the

PWM output duty is 100%.

•

16-bit STM, PWM Mode, Edge-aligned Mode, TnDPX=1

CCRP

1~255

0

Period

CCR�

D�ty

CCRP

×

�56

65536

The PWM output period is determined by the CCRA register value together with the TM clock while

the PWM duty cycle is defined by the (CCRP×256) value except when the CCRP value is equal to 0.