Rev. 1.50

1�4

����st ��� �01�

Rev. 1.50

1�5

����st ��� �01�

HT66F0175/HT66F0185

A/D Flash MCU with EEPROM

HT66F0175/HT66F0185

A/D Flash MCU with EEPROM

The clock source for the A/D converter, which originates from the system clock f

SYS

, can be chosen

to be either f

SYS

or a subdivided version of f

SYS

. The division ratio value is determined by the

SACKS2~SACKS0 bits in the SADC1 register. Although the A/D clock source is determined by the

system clock f

SYS

and by bits SACKS2~SACKS0, there are some limitations on the maximum A/D

clock source speed that can be selected. As the recommended range of permissible A/D clock period,

t

ADCK

, is from 0.5μs to 10μs, care must be taken for system clock frequencies. For example, as the

system clock operates at a frequency of 8MHz, the SACKS2~SACKS0 bits should not be set to 000,

001 or 111. Doing so will give A/D clock periods that are less than the minimum A/D clock period

which may result in inaccurate A/D conversion values. Refer to the following table for examples,

where values marked with an asterisk * show where, depending upon the devices, special care must

be taken, as the values may be less than the specified minimum A/D Clock Period.

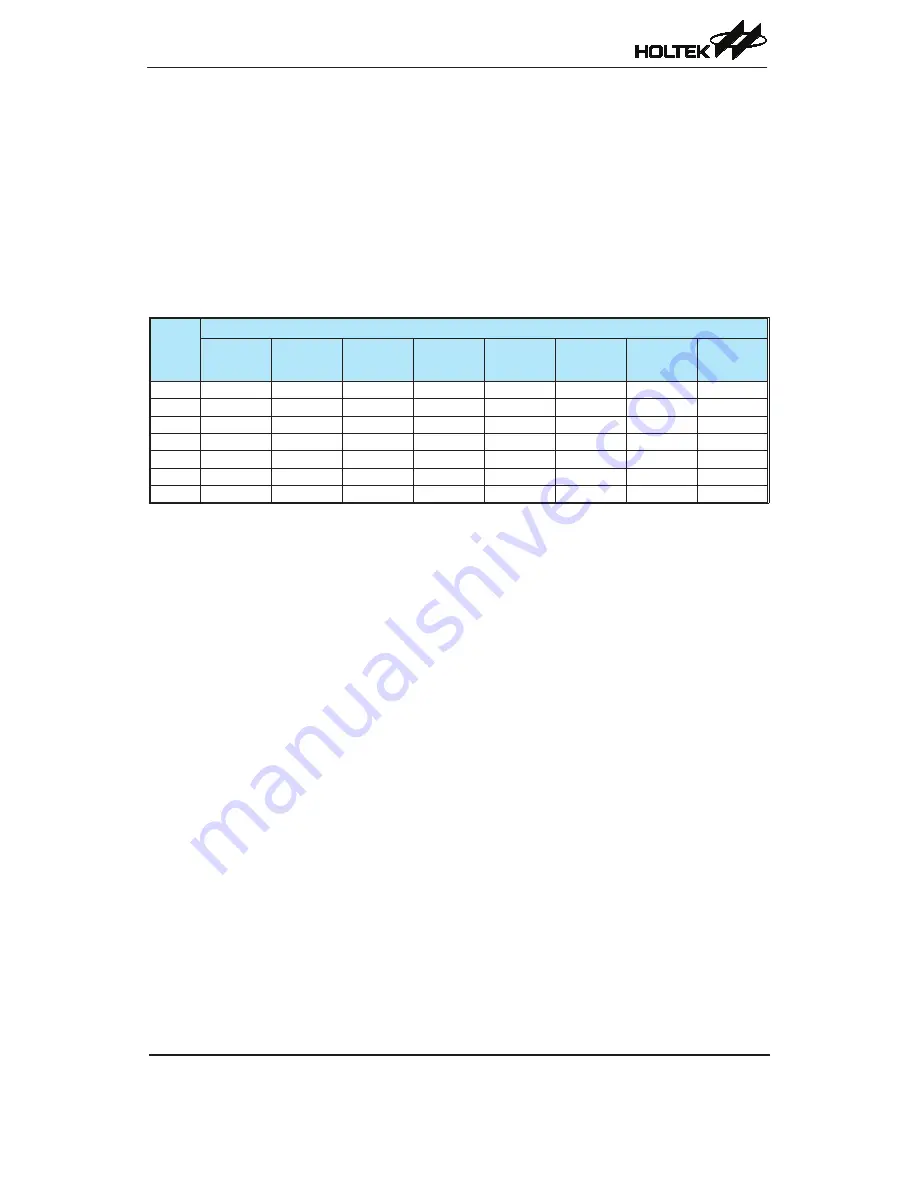

f

SYS

A/D Clock Period (t

ADCK

)

SACKS[2:0]

= 000

(f

SYS

)

SACKS[2:0]

= 001

(f

SYS

/2)

SACKS[2:0]

= 010

(f

SYS

/4)

SACKS[2:0]

= 011

(f

SYS

/8)

SACKS[2:0]

= 100

(f

SYS

/16)

SACKS[2:0]

= 101

(f

SYS

/32)

SACKS[2:0]

= 110

(f

SYS

/64)

SACKS[2:0]

= 111

(f

SYS

/128)

1 MHz

1μs

2μs

4μs

8μs

16μs *

32μs *

64μs *

128μs *

� MHz

500ns

1μs

2μs

4μs

8μs

16μs *

32μs *

64μs *

4 MHz

250ns *

500ns

1μs

2μs

4μs

8μs

16μs *

32μs *

� MHz

125ns *

250ns *

500ns

1μs

2μs

4μs

8μs

16μs *

1� MHz

83ns *

167ns *

333ns *

66�ns

1.33μs

2.67μs

5.33μs

10.67μs *

16 MHz

62.5ns *

125ns *

250ns *

500ns

1μs

2μs

4μs

8μs

�0 MHz

50ns *

100ns *

200ns *

400ns *

�00ns

1.6μs

3.2μs

6.4μs

A/D Clock Period Examples

Controlling the power on/off function of the A/D converter circuitry is implemented using the

ADCEN bit in the SADC0 register. This bit must be set high to power on the A/D converter. When

the ADCEN bit is set high to power on the A/D converter internal circuitry, a certain delay, as

indicated in the timing diagram, must be allowed before an A/D conversion is initiated. Even if

no pins are selected for use as A/D inputs, if the ADCEN bit is high, then some power will still be

consumed. In power conscious applications it is therefore recommended that the ADCEN is set low

to reduce power consumption when the A/D converter function is not being used.

Conversion Rate and Timing Diagram

A complete A/D conversion contains two parts, data sampling and data conversion. The data

sampling which is defined as t

ADS

takes 4 A/D clock cycles and the data conversion takes 12 A/D

clock cycles. Therefore a total of 16 A/D clock cycles for an A/D conversion which is defined as t

ADC

are necessary.

Maximum single A/D conversion rate = A/D clock period / 16 (1)

The accompanying diagram shows graphically the various stages involved in an analog to digital

conversion process and its associated timing. After an A/D conversion process has been initiated

by the application program, the microcontroller internal hardware will begin to carry out the

conversion, during which time the program can continue with other functions. The time taken for the

A/D conversion is 16 t

ADCK

clock cycles where t

ADCK

is equal to the A/D clock period.