Rev. 1.50

156

����st ��� �01�

Rev. 1.50

15�

����st ��� �01�

HT66F0175/HT66F0185

A/D Flash MCU with EEPROM

HT66F0175/HT66F0185

A/D Flash MCU with EEPROM

UART External Pin

To communicate with an external serial interface, the internal UART has two external pins known

as TX and RX. The TX and RX pins are respectively the UART transmitter and receiver pins which

are pin-shared with I/O or other pin-shared functions. Along with the UARTEN bit, the TXEN and

RXEN bits, if set, will automatically setup these I/O pins to their respective TX output and RX input

conditions and disable any pull-high resistor option which may exist on the TX and RX pins. When

the TX or RX pin function is disabled by clearing the UARTEN, TXEN or RXEN bit, the TX or RX

pin will be used as I/O or other pin-shared functional pin depending upon the pin-shared function

priority.

UART Data Transfer Scheme

The above diagram shows the overall data transfer structure arrangement for the UART interface.

The actual data to be transmitted from the MCU is first transferred to the TXR register by the

application program. The data will then be transferred to the Transmit Shift Register from where it

will be shifted out, LSB first, onto the TX pin at a rate controlled by the Baud Rate Generator. Only

the TXR register is mapped onto the MCU Data Memory, the Transmit Shift Register is not mapped

and is therefore inaccessible to the application program.

Data to be received by the UART is accepted on the external RX pin, from where it is shifted in,

LSB first, to the Receiver Shift Register at a rate controlled by the Baud Rate Generator. When

the shift register is full, the data will then be transferred from the shift register to the internal RXR

register, where it is buffered and can be manipulated by the application program. Only the TXR

register is mapped onto the MCU Data Memory, the Receiver Shift Register is not mapped and is

therefore inaccessible to the application program.

It should be noted that the actual register for data transmission and reception, although referred to

in the text, and in application programs, as separate TXR and RXR registers, only exists as a single

shared register in the Data Memory. This shared register known as the TXR_RXR register is used

for both data transmission and data reception.

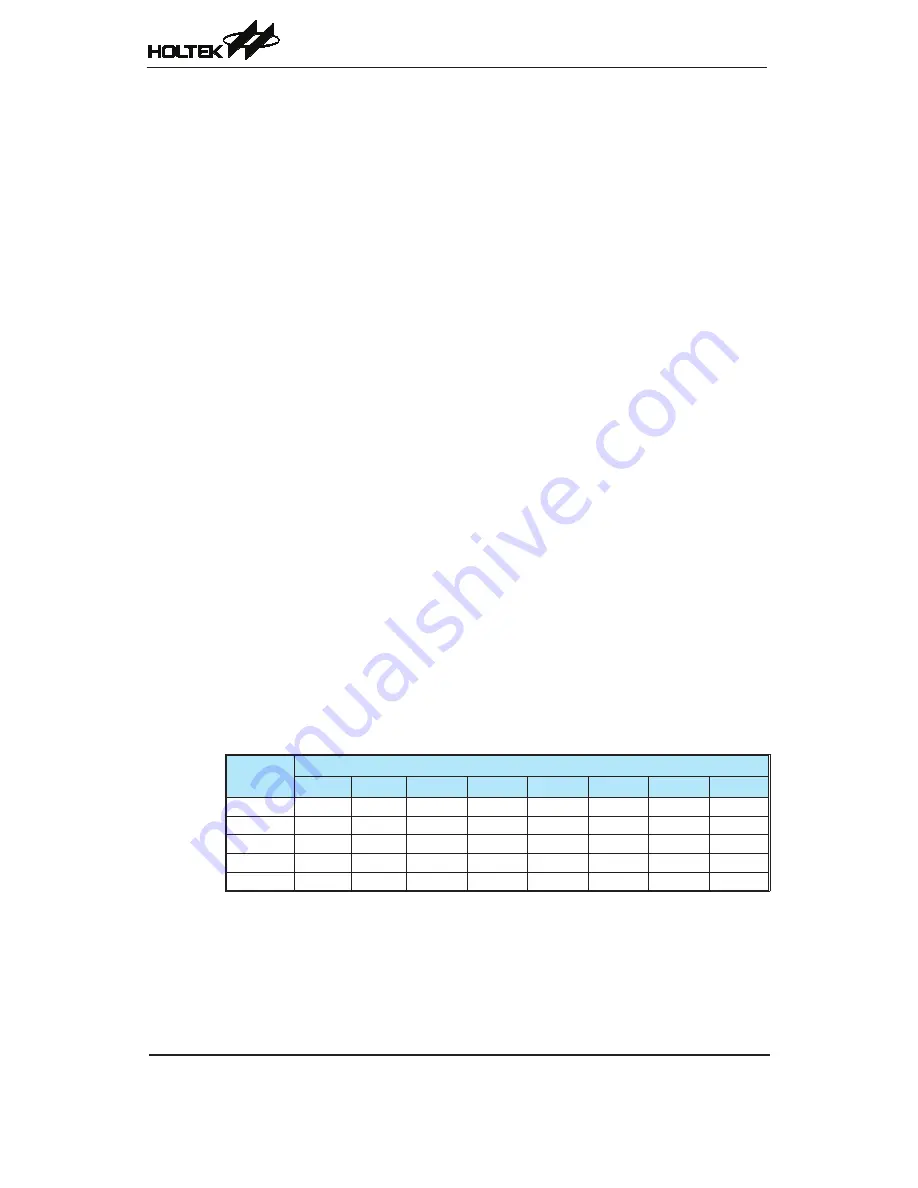

UART Status and Control Registers

There are five control registers associated with the UART function. The USR, UCR1 and UCR2

registers control the overall function of the UART, while the BRG register controls the Baud rate.

The actual data to be transmitted and received on the serial interface is managed through the TXR_

RXR data registers.

Register

Name

Bit

7

6

5

4

3

2

1

0

USR

PERR

NF

FERR

OERR

RIDLE

RXIF

TIDLE

TXIF

UCR1

U�RTEN

BNO

PREN

PRT

STOPS

TXBRK

RX�

TX�

UCR�

TXEN

RXEN

BRGH

�DDEN

W�KE

RIE

TIIE

TEIE

BRG

BRG�

BRG6

BRG5

BRG4

BRG3

BRG�

BRG1

BRG0

TXR_RXR TXRX�

TXRX6

TXRX5

TXRX4

TXRX3

TXRX�

TXRX1

TXRX0

UART Status and Control Registers List – HT66F0185 only