Rev. 1.50

1��

����st ��� �01�

Rev. 1.50

1�3

����st ��� �01�

HT66F0175/HT66F0185

A/D Flash MCU with EEPROM

HT66F0175/HT66F0185

A/D Flash MCU with EEPROM

A/D Converter Interrupt

The A/D Converter Interrupt is controlled by the termination of an A/D conversion process. An A/D

Converter Interrupt request will take place when the A/D Converter Interrupt request flag, ADF, is

set, which occurs when the A/D conversion process finishes. To allow the program to branch to its

respective interrupt vector address, the global interrupt enable bit, EMI, and A/D Interrupt enable bit,

ADE, must first be set. When the interrupt is enabled, the stack is not full and the A/D conversion

process has ended, a subroutine call to the A/D Converter Interrupt vector, will take place. When the

interrupt is serviced, the A/D Converter Interrupt flag, ADF, will be automatically cleared. The EMI

bit will also be automatically cleared to disable other interrupts.

Time Base Interrupt

The function of the Time Base Interrupts is to provide regular time signal in the form of an internal

interrupt. They are controlled by the overflow signals from their respective timer functions. When

these happens their respective interrupt request flags, TB0F or TB1F will be set. To allow the

program to branch to their respective interrupt vector addresses, the global interrupt enable bit, EMI

and Time Base enable bits, TB0E or TB1E, must first be set. When the interrupt is enabled, the stack

is not full and the Time Base overflows, a subroutine call to their respective vector locations will

take place. When the interrupt is serviced, the respective interrupt request flag, TB0F or TB1F, will

be automatically reset and the EMI bit will be cleared to disable other interrupts. The purpose of

the Time Base Interrupt is to provide an interrupt signal at fixed time periods. Their clock sources

originate from the internal clock source f

TB

. This f

TB

input clock passes through a divider, the

division ratio of which is selected by programming the appropriate bits in the TBC register to obtain

longer interrupt periods whose value ranges. The clock source that generates f

TB

, which in turn

controls the Time Base interrupt period, can originate from several different sources, as shown in the

System Operating Mode section.

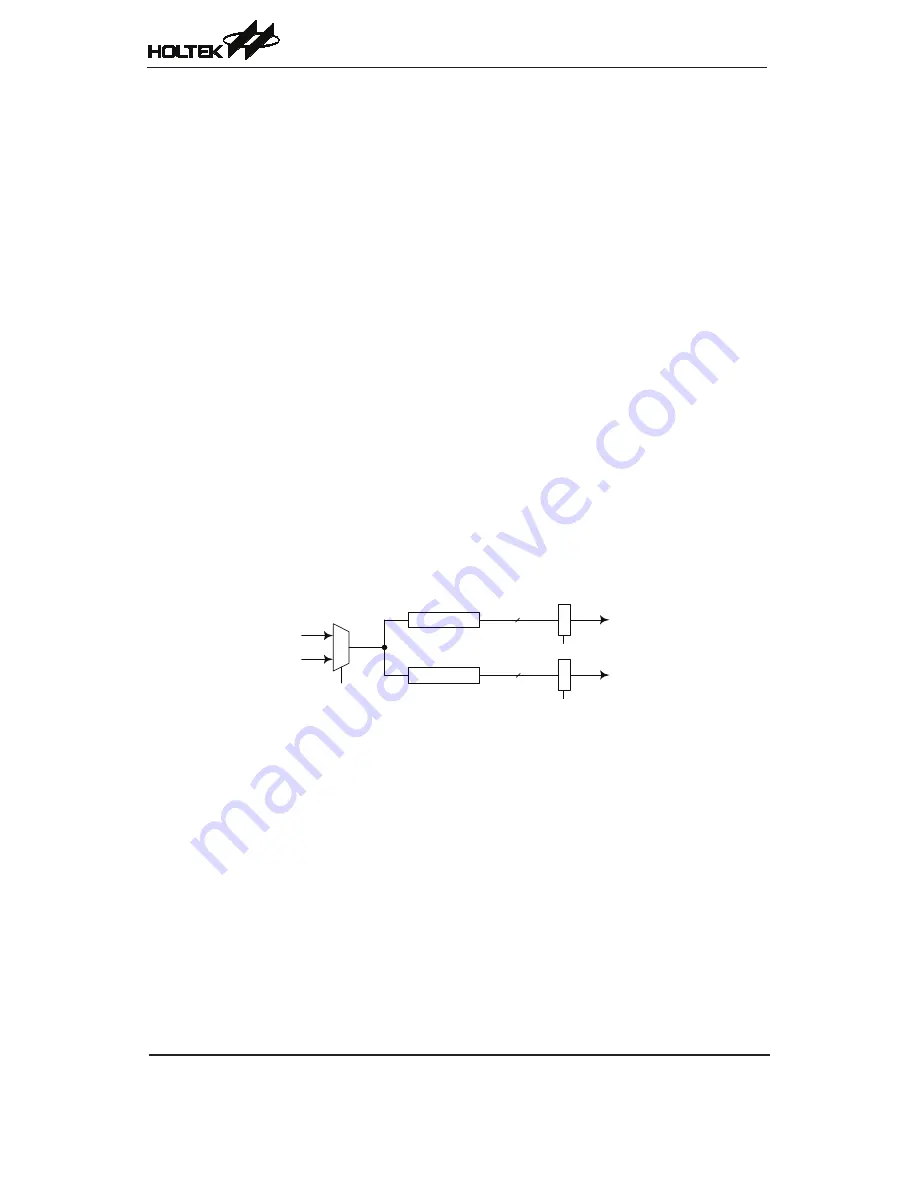

M

U

X

f

SYS

/4

f

TBC

Prescaler

TBCK

f

TB

f

TB

/�

�

~ f

TB

/�

15

M

U

X

TB11~TB10

Time Base 0 Interr�pt

Time Base 1 Interr�pt

TB0�~TB00

Prescaler

M

U

X

f

TB

/�

1�

~ f

TB

/�

15

Time Base Interrupts