Rev. 2.10

11�

���� 02� 201�

Rev. 2.10

115

���� 02� 201�

HT68F20/HT68F30/HT68F40/HT68F50/HT68F60

HT68FU30/HT68FU40/HT68FU50/HT68FU60

Enhanced I/O Flash Type 8-Bit MCU with EEPROM

HT68F20/HT68F30/HT68F40/HT68F50/HT68F60

HT68FU30/HT68FU40/HT68FU50/HT68FU60

Enhanced I/O Flash Type 8-Bit MCU with EEPROM

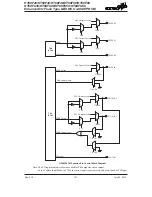

Compact Type TM Operating Modes

The Compact Type TM can operate in one of three operating modes, Compare Match Output Mode,

PWM Mode or Timer/Counter Mode. The operating mode is selected using the TnM1 and TnM0

bits in the TMnC1 register.

Compare Match Output Mode

To select this mode, bits TnM1 and TnM0 in the TMnC1 register, should be set to "00" respectively.

In this mode once the counter is enabled and running it can be cleared by three methods. These are

a counter overflow, a compare match from Comparator A and a compare match from Comparator P.

When the TnCCLR bit is low, there are two ways in which the counter can be cleared. One is when

a compare match occurs from Comparator P, the other is when the CCRP bits are all zero which

allows the counter to overflow. Here both TnAF and TnPF interrupt request flags for the Comparator

A and Comparator P respectively, will both be generated.

If the TnCCLR bit in the TMnC1 register is high then the counter will be cleared when a compare

match occurs from Comparator A. However, here only the TnAF interrupt request flag will be

generated even if the value of the CCRP bits is less than that of the CCRA registers. Therefore when

TnCCLR is high no TnPF interrupt request flag will be generated. If the CCRA bits are all zero, the

counter will overflow when its reaches its maximum 10-bit, 3FF Hex, value, however here the TnAF

interrupt request flag will not be generated.

As the name of the mode suggests, after a comparison is made, the TM output pin will change state.

The TM output pin condition however only changes state when an TnAF interrupt request flag

is generated after a compare match occurs from Comparator A. The TnPF interrupt request flag,

generated from a compare match occurs from Comparator P, will have no effect on the TM output

pin. The way in which the TM output pin changes state are determined by the condition of the

TnIO1 and TnIO0 bits in the TMnC1 register. The TM output pin can be selected using the TnIO1

and TnIO0 bits to go high, to go low or to toggle from its present condition when a compare match

occurs from Comparator A. The initial condition of the TM output pin, which is setup after the

TnON bit changes from low to high, is setup using the TnOC bit. Note that if the TnIO1 and TnIO0

bits are zero then no pin change will take place.

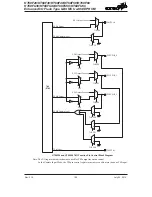

Timer/Counter Mode

To select this mode, bits TnM1 and TnM0 in the TMnC1 register should be set to 11 respectively.

The Timer/Counter Mode operates in an identical way to the Compare Match Output Mode

generating the same interrupt flags. The exception is that in the Timer/Counter Mode the TM output

pin is not used. Therefore the above description and Timing Diagrams for the Compare Match

Output Mode can be used to understand its function. As the TM output pin is not used in this mode,

the pin can be used as a normal I/O pin or other pin-shared function.