Rev. 2.10

116

���� 02� 201�

Rev. 2.10

117

���� 02� 201�

HT68F20/HT68F30/HT68F40/HT68F50/HT68F60

HT68FU30/HT68FU40/HT68FU50/HT68FU60

Enhanced I/O Flash Type 8-Bit MCU with EEPROM

HT68F20/HT68F30/HT68F40/HT68F50/HT68F60

HT68FU30/HT68FU40/HT68FU50/HT68FU60

Enhanced I/O Flash Type 8-Bit MCU with EEPROM

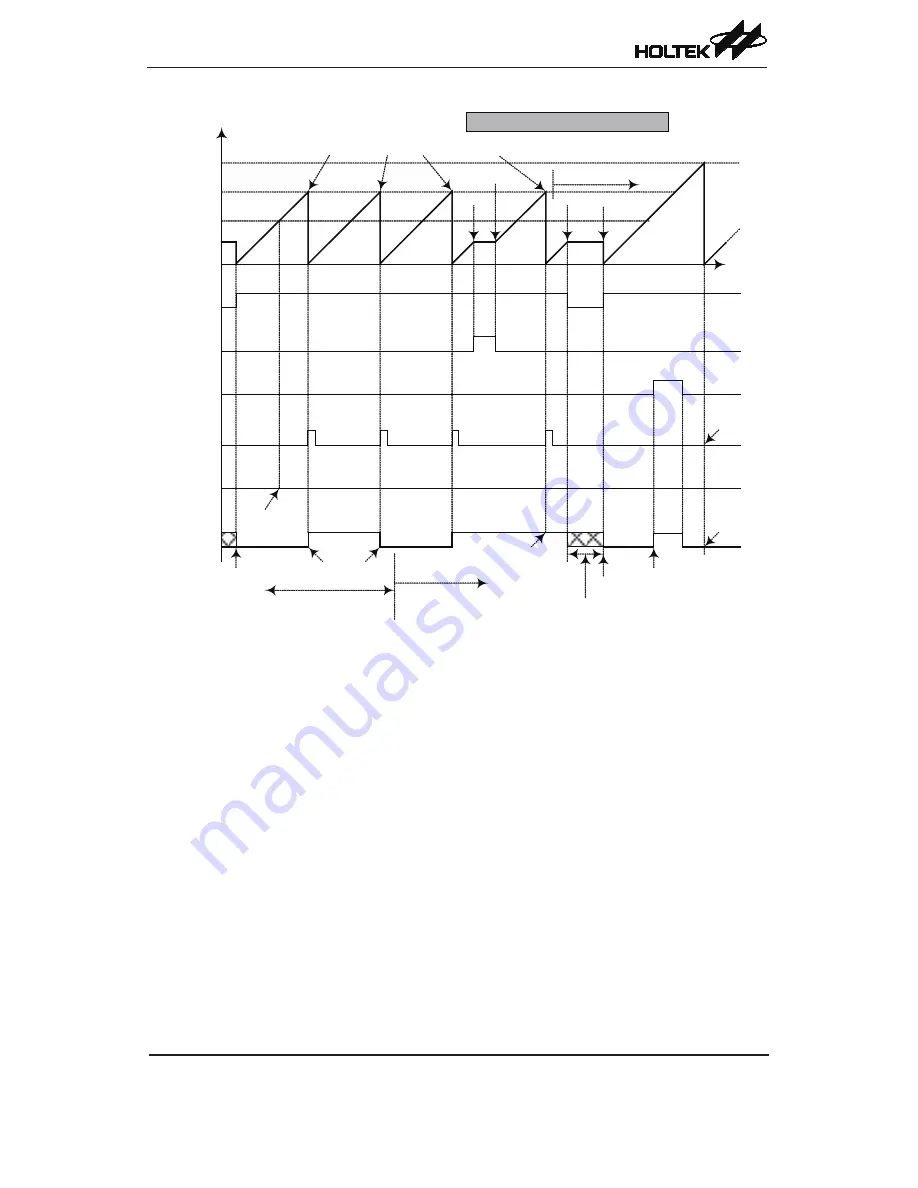

Co�nter Va��e

0x3FF

CCRP

CCRA

TnON

TnPAU

TnPOL

CCRP Int.

F�ag TnPF

CCRA Int.

F�ag TnAF

TM O/P Pin

Time

CCRA=0

CCRA = 0

Co�nter overf�ow

CCRA > 0 Co�nter c�eared b� CCRA va��e

Pa�se

Res�me

Stop

Co�nter Restart

TnCCLR = 1; TnM [1:0] = 00

O�tp�t pin set to

initia� Leve� Low

if TnOC=0

O�tp�t Togg�e with

TnAF f�ag

Note TnIO [1:0] = 10

Active High O�tp�t se�ect

Here TnIO [1:0] = 11

Togg�e O�tp�t se�ect

O�tp�t not affected b�

TnAF f�ag. Remains High

�nti� reset b� TnON bit

O�tp�t Pin

Reset to Initia� va��e

O�tp�t contro��ed b�

other pin-shared f�nction

O�tp�t Inverts

when TnPOL is high

TnPF not

generated

No TnAF f�ag

generated on

CCRA overf�ow

O�tp�t does

not change

Compare Match Output Mode -- TnCCLR=1

Note: 1. With TnCCLR=1, a Comparator A match will clear the counter

2. The TM output pin is controlled only by the TnAF flag

3. The output pin is reset to its initial state by a TnON bit rising edge

4. The TnPF flag is not generated when TnCCLR=1