Rev. 2.10

17�

���� 02� 201�

Rev. 2.10

175

���� 02� 201�

HT68F20/HT68F30/HT68F40/HT68F50/HT68F60

HT68FU30/HT68FU40/HT68FU50/HT68FU60

Enhanced I/O Flash Type 8-Bit MCU with EEPROM

HT68F20/HT68F30/HT68F40/HT68F50/HT68F60

HT68FU30/HT68FU40/HT68FU50/HT68FU60

Enhanced I/O Flash Type 8-Bit MCU with EEPROM

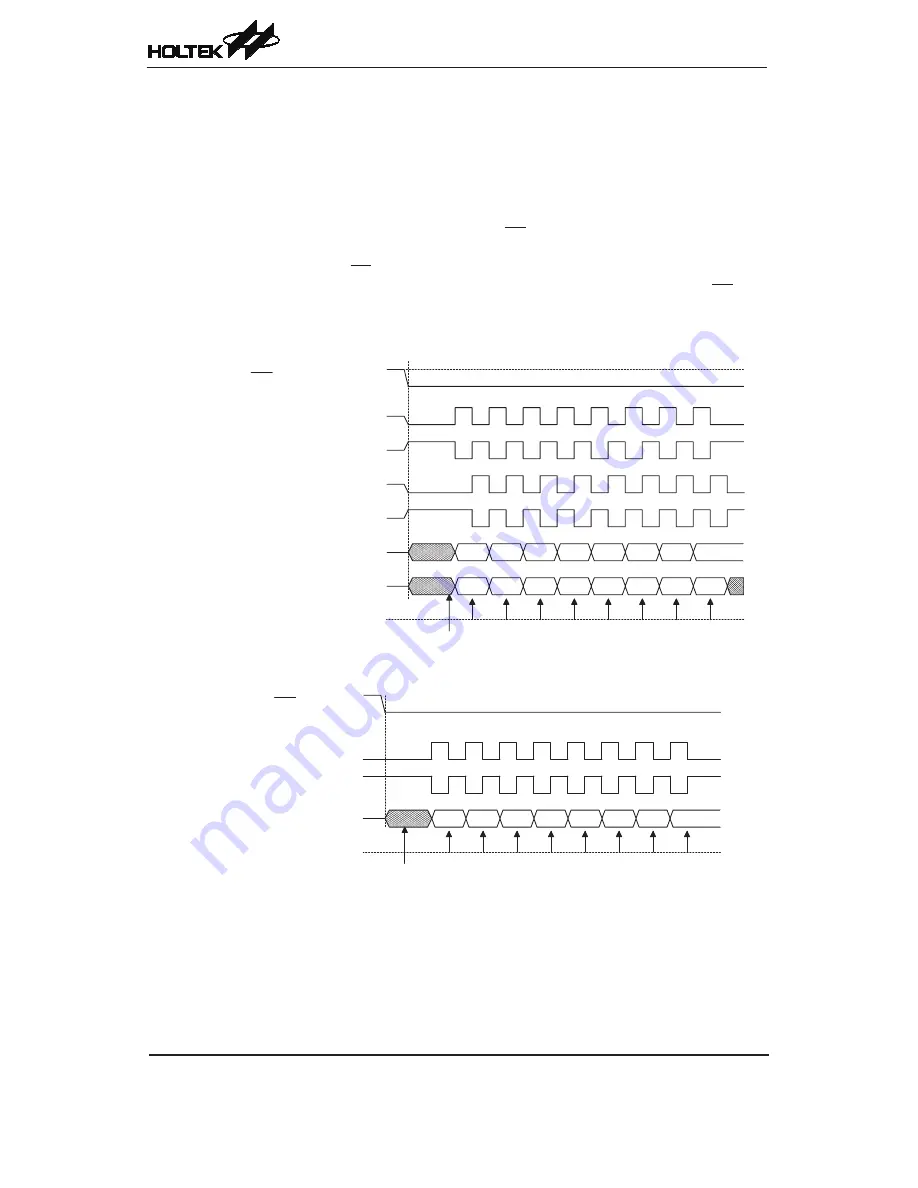

SPI Communication

After the SPI interface is enabled by setting the SIMEN bit high, then in the Master Mode, when

data is written to the SIMD register, transmission/reception will begin simultaneously. When the

data transfer is complete, the TRF flag will be set automatically, but must be cleared using the

application program. In the Slave Mode, when the clock signal from the master has been received,

any data in the SIMD register will be transmitted and any data on the SDI pin will be shifted into

the SIMD register. The master should output an SCS signal to enable the slave device before a

clock signal is provided. The slave data to be transferred should be well prepared at the appropriate

moment relative to the SCS signal depending upon the configurations of the CKPOLB bit and CKEG

bit. The accompanying timing diagram shows the relationship between the slave data and SCS signal

for various configurations of the CKPOLB and CKEG bits.

The SPI will continue to function even in the IDLE Mode.

SPI Master Mode Timing

SPI Slave Mode Timing – CKEG=0