Rev. 2.10

182

���� 02� 201�

Rev. 2.10

183

���� 02� 201�

HT68F20/HT68F30/HT68F40/HT68F50/HT68F60

HT68FU30/HT68FU40/HT68FU50/HT68FU60

Enhanced I/O Flash Type 8-Bit MCU with EEPROM

HT68F20/HT68F30/HT68F40/HT68F50/HT68F60

HT68FU30/HT68FU40/HT68FU50/HT68FU60

Enhanced I/O Flash Type 8-Bit MCU with EEPROM

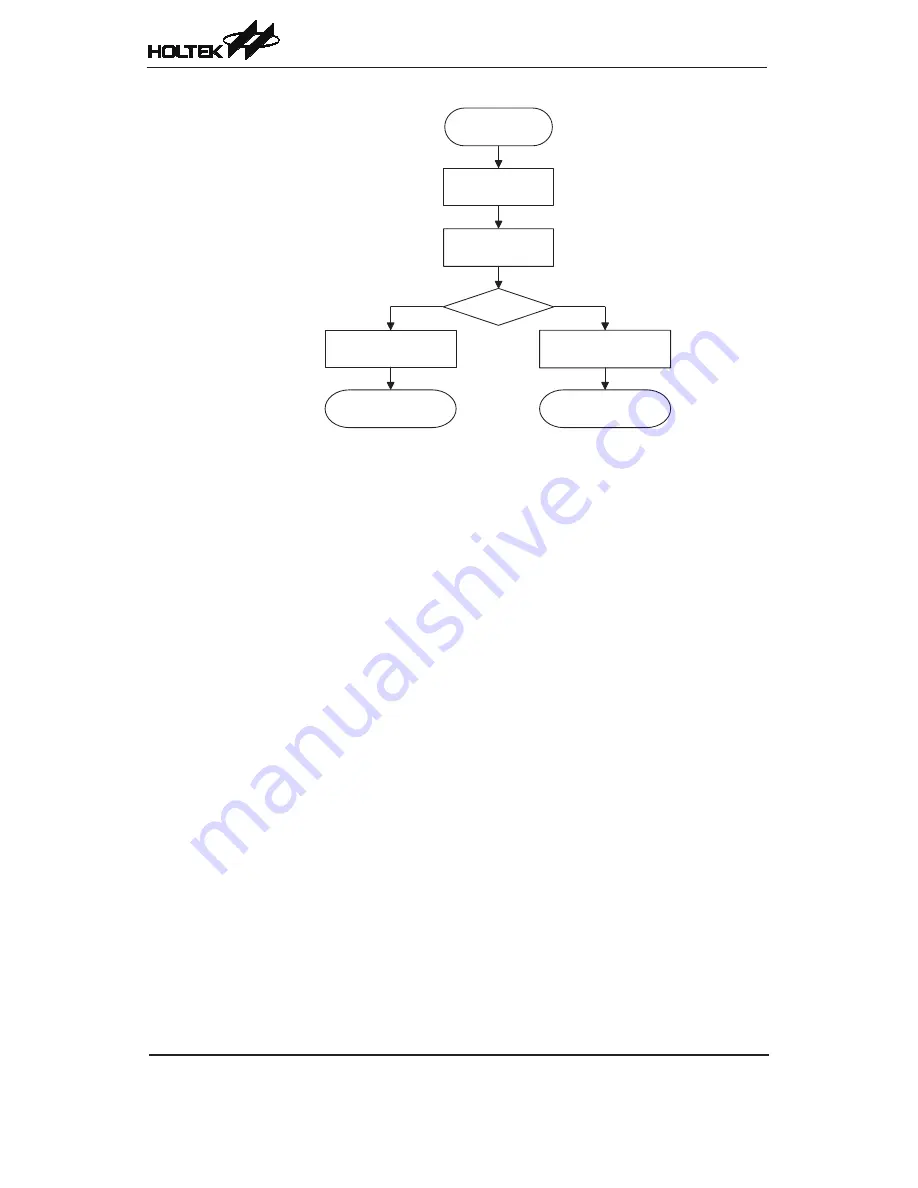

I

2

C Bus Initialisation Flow Chart

I

2

C Bus Start Signal

The START signal can only be generated by the master device connected to the I

2

C bus and not by

the slave device. This START signal will be detected by all devices connected to the I

2

C bus. When

detected, this indicates that the I

2

C bus is busy and therefore the HBB bit will be set. A START

condition occurs when a high to low transition on the SDA line takes place when the SCL line

remains high.

Slave Address

The transmission of a START signal by the master will be detected by all devices on the I

2

C bus.

To determine which slave device the master wishes to communicate with, the address of the slave

device will be sent out immediately following the START signal. All slave devices, after receiving

this 7-bit address data, will compare it with their own 7-bit slave address. If the address sent out by

the master matches the internal address of the microcontroller slave device, then an internal I

2

C bus

interrupt signal will be generated. The next bit following the address, which is the 8th bit, defines

the read/write status and will be saved to the SRW bit of the SIMC1 register. The slave device will

then transmit an acknowledge bit, which is a low level, as the 9th bit. The slave device will also set

the status flag HAAS when the addresses match.

As an I

2

C bus interrupt can come from two sources, when the program enters the interrupt

subroutine, the HAAS bit should be examined to see whether the interrupt source has come from

a matching slave address or from the completion of a data byte transfer. When a slave address is

matched, the device must be placed in either the transmit mode and then write data to the SIMD

register, or in the receive mode where it must implement a dummy read from the SIMD register to

release the SCL line.