Rev. 2.10

20�

���� 02� 201�

Rev. 2.10

205

���� 02� 201�

HT68F20/HT68F30/HT68F40/HT68F50/HT68F60

HT68FU30/HT68FU40/HT68FU50/HT68FU60

Enhanced I/O Flash Type 8-Bit MCU with EEPROM

HT68F20/HT68F30/HT68F40/HT68F50/HT68F60

HT68FU30/HT68FU40/HT68FU50/HT68FU60

Enhanced I/O Flash Type 8-Bit MCU with EEPROM

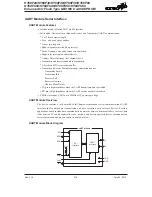

External Interrupt

The external interrupts are controlled by signal transitions on the pins INT0~INT3. An external

interrupt request will take place when the external interrupt request flags, INT0F~INT3F, are set,

which will occur when a transition, whose type is chosen by the edge select bits, appears on the

external interrupt pins. To allow the program to branch to its respective interrupt vector address, the

global interrupt enable bit, EMI, and respective external interrupt enable bit, INT0E~INT3E, must

first be set. Additionally the correct interrupt edge type must be selected using the INTEG register to

enable the external interrupt function and to choose the trigger edge type. As the external interrupt

pins are pin-shared with I/O pins, they can only be configured as external interrupt pins if their

external interrupt enable bit in the corresponding interrupt register has been set. The pin must also

be setup as an input by setting the corresponding bit in the port control register. When the interrupt

is enabled, the stack is not full and the correct transition type appears on the external interrupt pin,

a subroutine call to the external interrupt vector, will take place. When the interrupt is serviced, the

external interrupt request flags, INT0F~INT3F, will be automatically reset and the EMI bit will be

automatically cleared to disable other interrupts. Note that any pull-high resistor selections on the

external interrupt pins will remain valid even if the pin is used as an external interrupt input.

The INTEG register is used to select the type of active edge that will trigger the external interrupt.

A choice of either rising or falling or both edge types can be chosen to trigger an external interrupt.

Note that the INTEG register can also be used to disable the external interrupt function.

Comparator Interrupt

The comparator interrupt is controlled by the two internal comparators. A comparator interrupt

request will take place when the comparator interrupt request flags, CP0F or CP1F, are set, a

situation that will occur when the comparator output changes state. To allow the program to branch

to its respective interrupt vector address, the global interrupt enable bit, EMI, and comparator

interrupt enable bits, CP0E and CP1E, must first be set. When the interrupt is enabled, the stack is

not full and the comparator inputs generate a comparator output transition, a subroutine call to the

comparator interrupt vector, will take place. When the interrupt is serviced, the external interrupt

request flags, will be automatically reset and the EMI bit will be automatically cleared to disable

other interrupts.