Rev. 2.10

78

���� 02� 201�

Rev. 2.10

79

���� 02� 201�

HT68F20/HT68F30/HT68F40/HT68F50/HT68F60

HT68FU30/HT68FU40/HT68FU50/HT68FU60

Enhanced I/O Flash Type 8-Bit MCU with EEPROM

HT68F20/HT68F30/HT68F40/HT68F50/HT68F60

HT68FU30/HT68FU40/HT68FU50/HT68FU60

Enhanced I/O Flash Type 8-Bit MCU with EEPROM

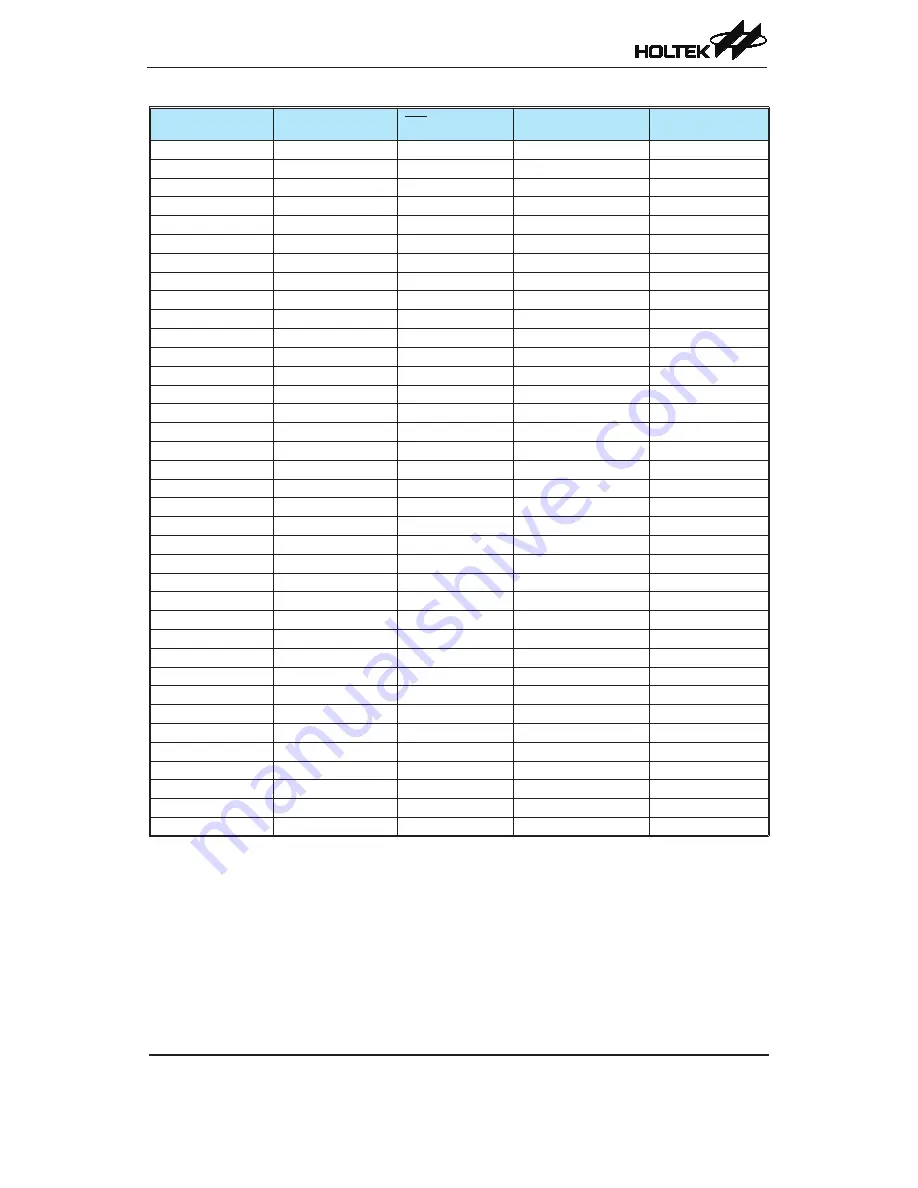

Register

Reset (Power-on)

RES or LVR Reset

WDT Time-out

(Normal Operation)

WDT Time-out

(IDLE)

TM0C0

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

� � � � � � � �

TM0C1

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

� � � � � � � �

TM0DL

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

� � � � � � � �

TM0DH

- - - - - - 00

- - - - - - 00

- - - - - - 00

- - - - - - ��

TM0AL

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

� � � � � � � �

TM0AH

- - - - - - 00

- - - - - - 00

- - - - - - 00

- - - - - - ��

EEA

x x x x x x x x

x x x x x x x x

x x x x x x x x

� � � � � � � �

EED

x x x x x x x x

x x x x x x x x

x x x x x x x x

� � � � � � � �

EEC

- - - - 0000

- - - - 0000

- - - - 0000

- - - - ����

TMPC0

1001 - - 01

1001 - - 01

1001 - - 01

���� - - ��

TMPC1

- - 01 - - 01

- - 01 - - 01

- - 01 - - 01

- - �� - - ��

PRM0

- 0- 0 0000

- 0- 0 0000

- 0- 0 0000

- �- � ����

PRM1

0 0 0 - 0 0 0 0

0 0 0 - 0 0 0 0

0 0 0 - 0 0 0 0

� � � - � � � �

PRM2

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

� � � � � � � �

TM1C0

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

� � � � � � � �

TM1C1

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

� � � � � � � �

TM1C2

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

� � � � � � � �

TM1DL

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

� � � � � � � �

TM1DH

- - - - - - 00

- - - - - - 00

- - - - - - 00

- - - - - - ��

TM1AL

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

� � � � � � � �

TM1AH

- - - - - - 00

- - - - - - 00

- - - - - - 00

- - - - - - ��

TM1BL

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

� � � � � � � �

TM1BH

- - - - - - 00

- - - - - - 00

- - - - - - 00

- - - - - - ��

TM2C0

0 0 0 0 0 - - -

0 0 0 0 0 - - -

0 0 0 0 0 - - -

� � � � � - - -

TM2C1

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

� � � � � � � �

TM2DL

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

� � � � � � � �

TM2DH

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

� � � � � � � �

TM2AL

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

� � � � � � � �

TM2AH

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

� � � � � � � �

TM2RP

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

� � � � � � � �

TM3C0

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

� � � � � � � �

TM3C1

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

� � � � � � � �

TM3DL

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

� � � � � � � �

TM3DH

- - - - - -00

- - - - - -00

- - - - - -00

- - - - - -��

TM3AL

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

� � � � � � � �

TM3AH

- - - - - -00

- - - - - -00

- - - - - -00

- - - - - -��

SCOMC

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

� � � � � � � �

Note: "u" stands for unchanged

"x" stands for unknown

"–" stands for unimplemented