Rev. 2.10

32

���� 02� 201�

Rev. 2.10

33

���� 02� 201�

HT68F20/HT68F30/HT68F40/HT68F50/HT68F60

HT68FU30/HT68FU40/HT68FU50/HT68FU60

Enhanced I/O Flash Type 8-Bit MCU with EEPROM

HT68F20/HT68F30/HT68F40/HT68F50/HT68F60

HT68FU30/HT68FU40/HT68FU50/HT68FU60

Enhanced I/O Flash Type 8-Bit MCU with EEPROM

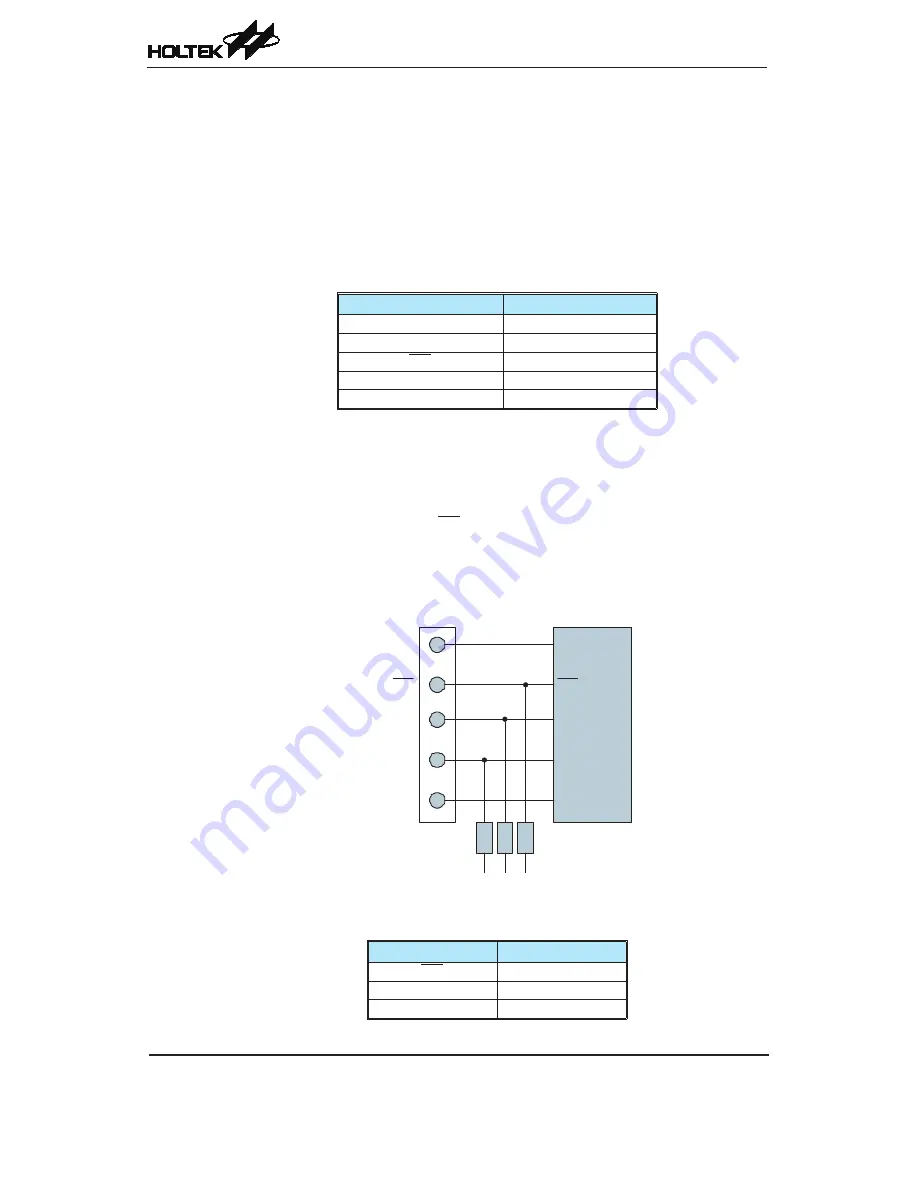

In Circuit Programming

The provision of Flash type Program Memory provides the user with a means of convenient and

easy upgrades and modifications to their programs on the same device.

As an additional convenience, Holtek has provided a means of programming the microcontroller

in-circuit using a 5-pin interface. This provides manufacturers with the possibility of manufacturing

their circuit boards complete with a programmed or un-programmed microcontroller, and then

programming or upgrading the program at a later stage. This enables product manufacturers to easily

keep their manufactured products supplied with the latest program releases without removal and

re-insertion of the device.

MCU Programming Pins

Function

PA0

Seria� Data Inp�t/O�tp�t

PA2

Seria� C�ock

RES

Device Reset

VDD

Power S�pp��

VSS

Gro�nd

The Program Memory and EEPROM data memory can both be programmed serially in-circuit using

this 5-wire interface. Data is downloaded and uploaded serially on a single pin with an additional

line for the clock. Two additional lines are required for the power supply and one line for the reset.

The technical details regarding the in-circuit programming of the devices are beyond the scope of

this document and will be supplied in supplementary literature.

During the programming process the RES pin will be held low by the programmer disabling the

normal operation of the microcontroller and taking control of the PA0 and PA2 I/O pins for data

and clock programming purposes. The user must there take care to ensure that no other outputs are

connected to these two pins.

*

*

*

W r i t e r _ V D D

R E S

D A T A

C L K

W r i t e r _ V S S

T o o t h e r C i r c u i t

D A T A

C L K

V S S

R E S

V D D

W r i t e r C o n n e c t o r

S i g n a l s

M C U P r o g r a m m i n g

P i n s

Note: * may be resistor or capacitor. The resistance of * must be greater than 1kΩ or the capacitance

of * must be less than 1nF.

Programmer Pin

MCU Pins

RES

PB0

DATA

PA0

CLK

PA2

Programmer and MCU Pins