Rev. 1.10

10

November 26, 2019

Rev. 1.10

11

November 26, 2019

HT68FB240

USB Low Speed Flash MCU

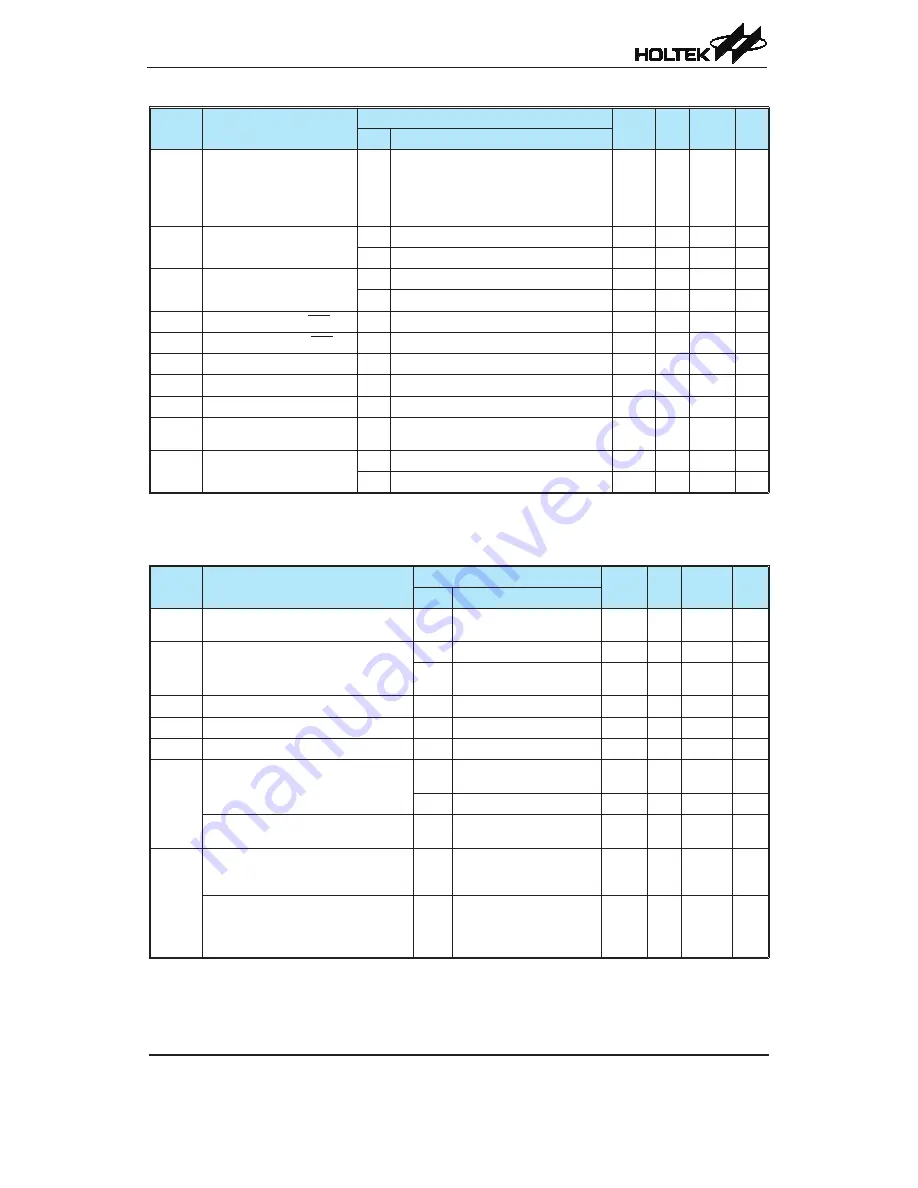

Symbol

Parameter

Test Conditions

Min. Typ. Max. Unit

V

DD

Conditions

I

SUS2

Suspend Current (Sleep 0)

(HIRC OSC, f

SYS

=off,

f

S

=f

SUB

=f

LIRC

)

5V

No load, system HALT, WDT disable,

LVR disable

USB transceiver, 3.3V Regulator off,

set SUSP2 (UCC.4) and set RCTRL

(UCC.7),Clear CLK_ADJ (SYSC.7=0)

—

220

300

μA

V

IL1

Input Low Voltage for I/O

Ports, TCK and INT

5V

—

0

─

0.3V

DD

V

— (Except V

DD

=5V)

0

─

0.2V

DD

V

V

IH1

Input High Voltage for I/O

Ports, TCK and INT

5V

—

0.7V

DD

─

V

DD

V

— (Except V

DD

=5V)

0.8V

DD

─

V

DD

V

V

IL2

Input Low Voltage (RES)

—

—

0

─

0.4V

DD

V

V

IH2

Input High Voltage (RES)

—

—

0.9V

DD

─

V

DD

V

I

OL

I/O Port Sink Current

5V V

OL

=0.4V

2

4

─

mA

I

OH

I/O Port Source Current

5V V

OH

=3.4V

-2

-4

─

mA

V

V33O

3.3V regulator output

5V I

V33O

=20mA

3.0

3.3

3.6

V

R

UDN

Pull-high Resistance

between UDN and V33O

3.3V

—

-5%

1.5

+5%

kΩ

R

PH

Pull-high Resistance of I/O

Ports

3V

—

20

60

100

kΩ

5V

—

10

30

50

kΩ

A.C. Characteristics

Ta= 25°C

Symbol

Parameter

Test Conditions

Min. Typ.

Max.

Unit

V

DD

Conditions

f

SYS

System clock (HIRC OSC)

USB mode (USB On)

4.2V~

5.5V Ta=25°C

-3%

12

+3%

MHz

f

LIRC

System clock (32K RC)

5V Ta=25°C

-10%

32

+10%

kHz

2.2V~

5.5V Ta=-40°C to 85°C

-50%

32

+60%

kHz

t

TCK

TCKn Input Pin Minimum Pulse Width

—

—

0.3

—

—

μs

t

RES

External Reset Minimum Low Pulse Width

—

—

10

—

—

μs

t

INT

Interrupt Minimum Pulse Width

—

—

10

—

—

μs

t

SST

System Start-up Timer Period

(Wake-up from HALT, f

SYS

off at HALT

state, Slow Mode → Normal Mode)

—

f

SYS

=HIRC

1024

—

—

t

SYS

—

f

SYS

=LIRC

2

—

—

t

SYS

System Start-up Timer Period (Wake-

up from HALT, f

SYS

on at HALT state)

—

—

2

—

—

t

SYS

t

RSTD

System Reset Delay Time (Power On

Reset, LVR reset, LVR S/W (LVRC)

reset, WDT S/W (WDTC) reset)

—

—

25

50

100

ms

System Reset Delay Time (Any Reset

except Power On Reset, LVR reset,

LVR S/W (LVRC) reset, WDT S/W

(WDTC) reset)

—

—

8.3

16.7

33.3

ms