Rev. 1.10

12

November 26, 2019

Rev. 1.10

13

November 26, 2019

HT68FB240

USB Low Speed Flash MCU

System Architecture

A key factor in the high-performance features of the Holtek range of microcontrollers is attributed to

their internal system architecture. The range of the device take advantage of the usual features found

within RISC microcontrollers providing increased speed of operation and enhanced performance.

The pipelining scheme is implemented in such a way that instruction fetching and instruction

execution are overlapped, hence instructions are effectively executed in one cycle, with the

exception of branch or call instructions. An 8-bit wide ALU is used in practically all instruction set

operations, which carries out arithmetic operations, logic operations, rotation, increment, decrement,

branch decisions, etc. The internal data path is simplified by moving data through the Accumulator

and the ALU. Certain internal registers are implemented in the Data Memory and can be directly

or indirectly addressed. The simple addressing methods of these registers along with additional

architectural features ensure that a minimum of external components is required to provide a

functional I/O control system with maximum reliability and flexibility. This makes the device

suitable for low-cost, high-volume production for controller applications.

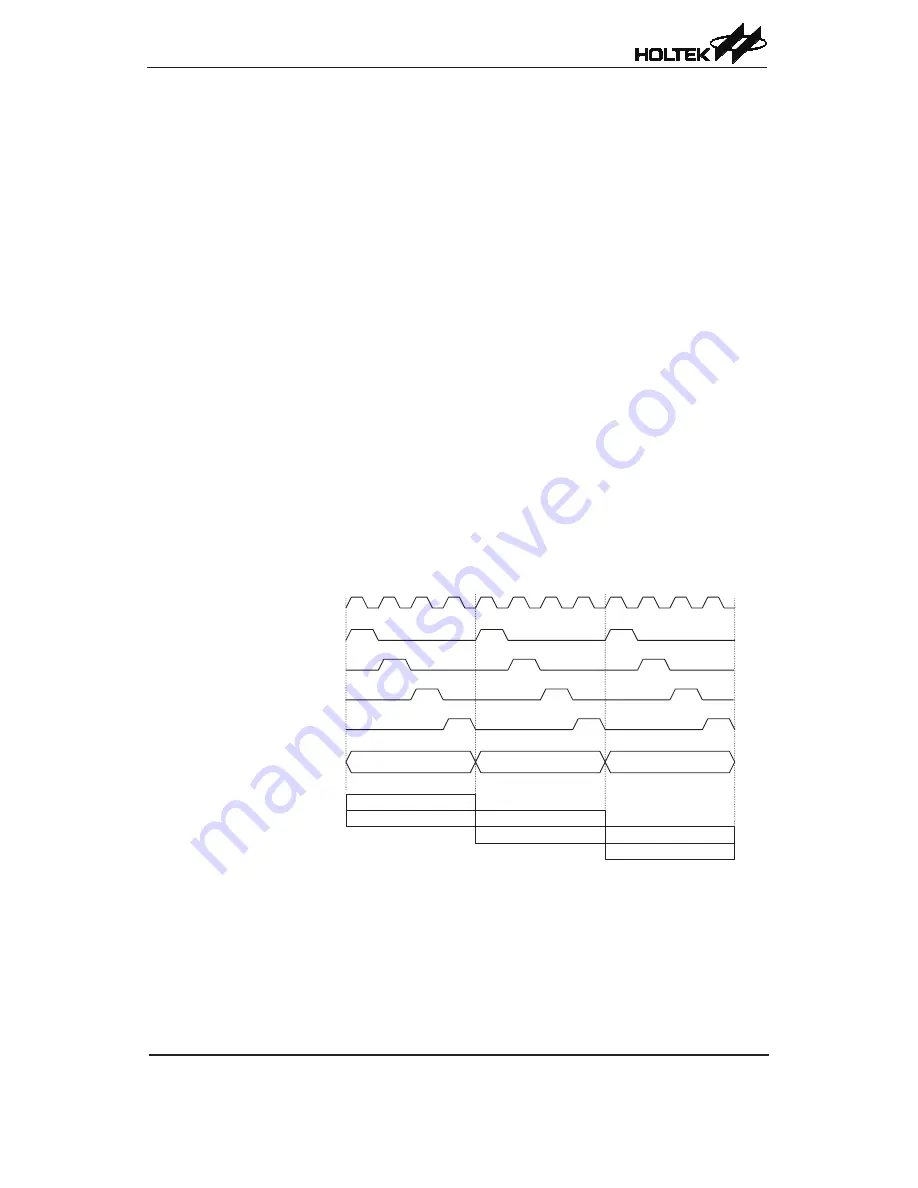

Clocking and Pipelining

The main system clock, derived from either a HIRC or LIRC oscillator is subdivided into four

internally generated non-overlapping clocks, T1~T4. The Program Counter is incremented at the

beginning of the T1 clock during which time a new instruction is fetched. The remaining T2~T4

clocks carry out the decoding and execution functions. In this way, one T1~T4 clock cycle forms

one instruction cycle. Although the fetching and execution of instructions takes place in consecutive

instruction cycles, the pipelining structure of the microcontroller ensures that instructions are

effectively executed in one instruction cycle. The exception to this are instructions where the

contents of the Program Counter are changed, such as subroutine calls or jumps, in which case the

instruction will take one more instruction cycle to execute.

System Clocking and Pipelining

For instructions involving branches, such as jump or call instructions, two machine cycles are

required to complete instruction execution. An extra cycle is required as the program takes one

cycle to first obtain the actual jump or call address and then another cycle to actually execute the

branch. The requirement for this extra cycle should be taken into account by programmers in timing

sensitive applications.