Rev. 1.10

36

November 26, 2019

Rev. 1.10

37

November 26, 2019

HT68FB240

USB Low Speed Flash MCU

SYSC Register

Bit

7

6

5

4

3

2

1

0

Name

CLK_ADJ

—

—

—

—

—

—

—

R/W

R/W

—

—

—

—

—

—

—

POR

1

—

—

—

—

—

—

—

Bit 7

CLK_ADJ:

Automatic Clock

a

djusts function

0: disable

1: enable

(default)

Note that if the user selects the HIRC as the system clock, the CLK_ADJ bit must be

set to "1" to adjust the clock frequency automatically.

Bit 6~0

Unimplemented, read as "0"

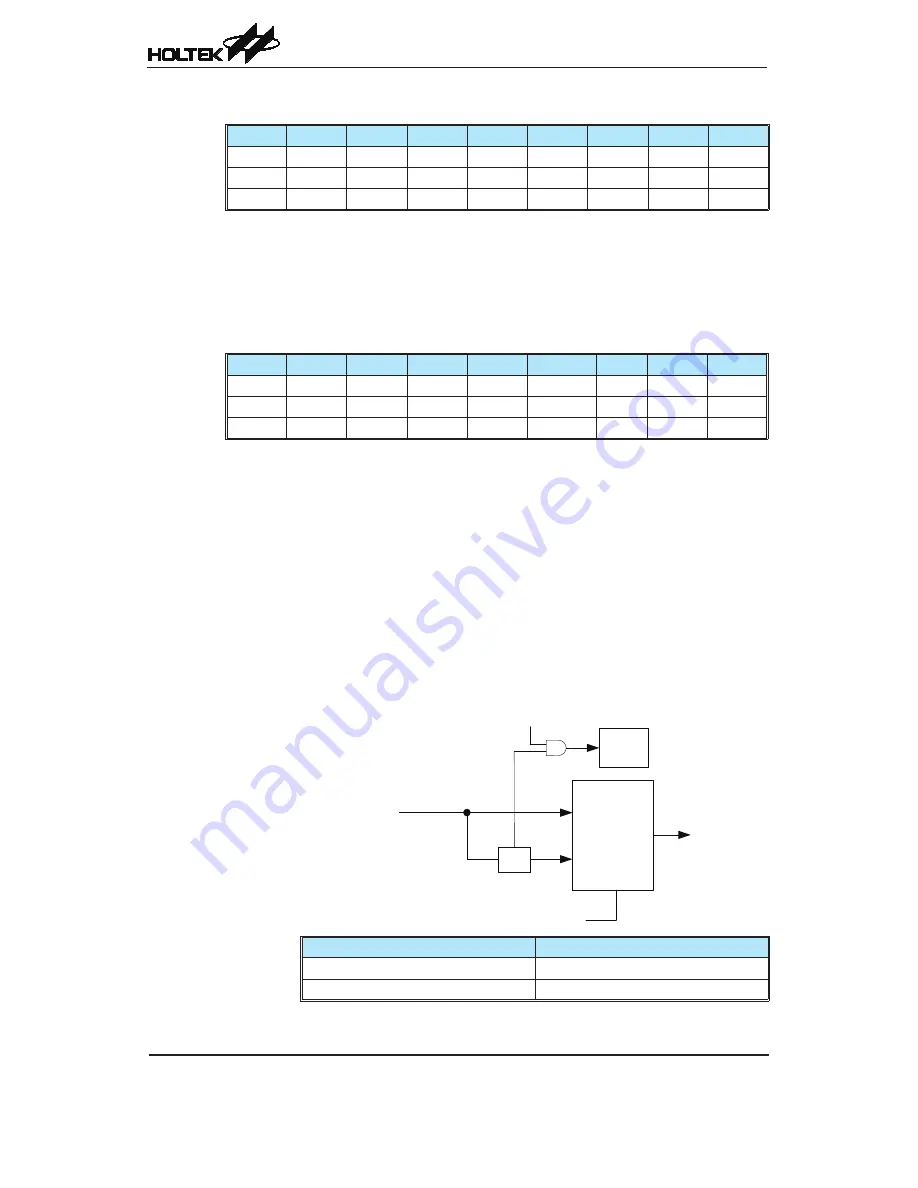

UCC Register

Bit

7

6

5

4

3

2

1

0

Name

Rctrl

SYSCLK

—

SUSP2 USBCKEN

—

EPS1

EPS0

R/W

R/W

R/W

—

R/W

R/W

—

R/W

R/W

POR

0

0

—

0

0

—

0

0

Bit 7

Rctrl:

7.5kΩ resistor between UDN and UBUS control bit

Described

elsewhere

Bit 6

SYSCLK:

Specify MCU oscillator frequency indication bit

0: 12MHz

1: 6MHz

Bit 5 U

nimplemented, read as "0"

Bit 4

SUSP2:

Reduce power consumption in suspend mode control bit

Described

elsewhere

Bit 3

USBCKEN:

USB clock control bit

0: disable

1: enable

Bit 2 U

nimplemented, read as "0"

Bit 1~0

EPS1, EPS0:

Accessing endpoint FIFO selection

Described

elsewhere

SYSCLK

6MHz

12MHz

USBCKEN

USB

SIE

f

H

MUX

(See Table)

HIRC

1/2

SYSCLK

f

H

0

12MHz

1

6MHz

High frequency system clock f

H

configure