Rev. 1.10

40

November 26, 2019

Rev. 1.10

41

November 26, 2019

HT68FB240

USB Low Speed Flash MCU

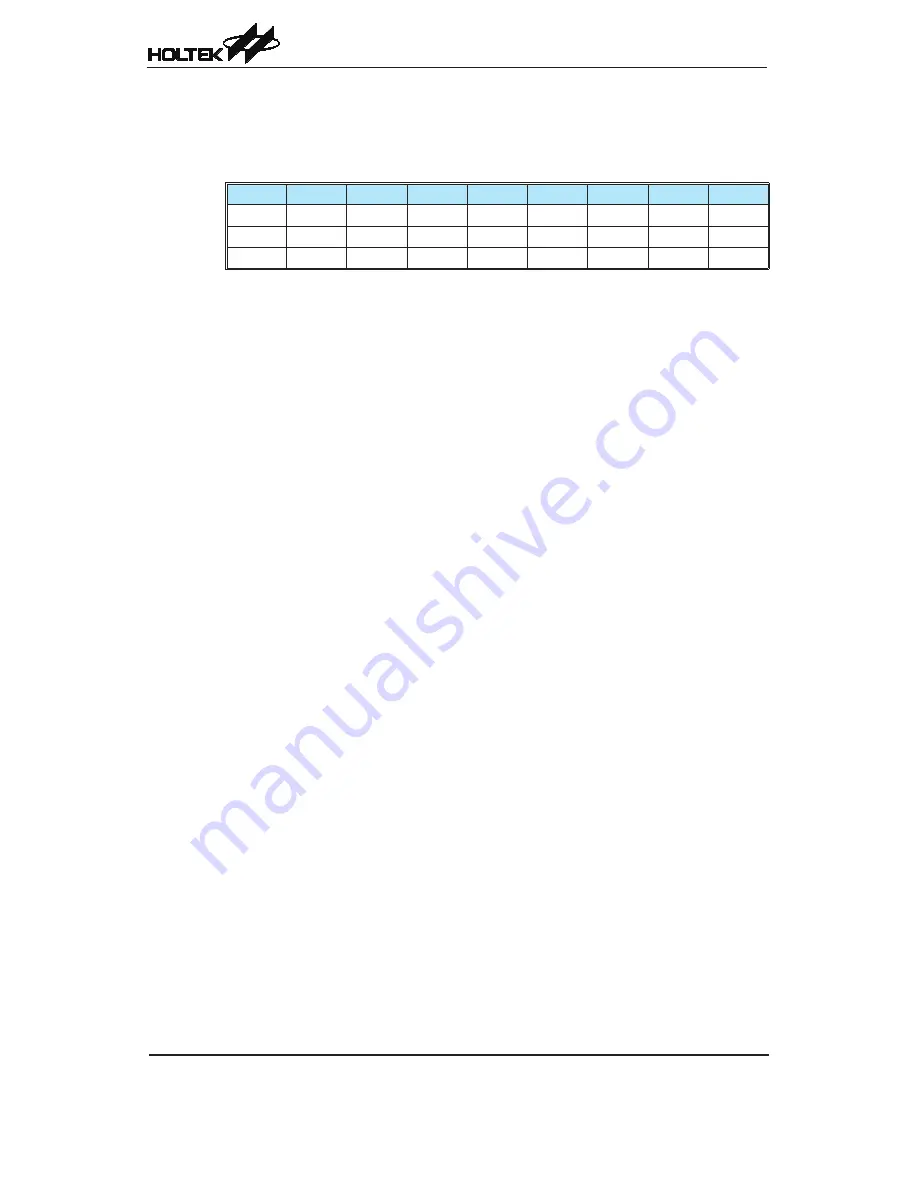

Control Register

A single register, SMOD, is used for overall control of the internal clocks within the device.

SMOD Register

Bit

7

6

5

4

3

2

1

0

Name

CKS2

CKS1

CKS0

—

LTO

HTO

IDLEN

HLCLK

R/W

R/W

R/W

R/W

—

R

R

R/W

R/W

POR

0

0

0

—

0

0

1

1

Bit 7~5

CKS2~CKS0:

The system clock selection when HLCLK is "0"

000: f

L

(f

LIRC

)

001: f

L

(f

LIRC

)

010: f

H

/64

011: f

H

/32

100: f

H

/16

101: f

H

/8

110: f

H

/4

111: f

H

/2

These three bits are used to select which clock is used as the system clock source. In

addition to the system clock source, which can be LIRC, a divided version of the high

speed system oscillator can also be chosen as the system clock source.

Bit 4

Unimplemented, read as "0"

Bit 3

LTO:

Low speed system oscillator ready flag

0: Not ready

1: Ready

This is the low speed system oscillator ready flag which indicates when the low speed

system oscillator is stable after power on reset or a wake-up has occurred. The flag

will be low when in the SLEEP0 Mode but after a wake-up has occurred, the flag will

change to a high level after 2 clock cycles if the LIRC oscillator is used.

Bit 2

HTO:

High speed system oscillator ready flag

0: Not ready

1: Ready

This is the high speed system oscillator ready flag which indicates when the high speed

system oscillator is stable. This flag is cleared to "0" by hardware when the device is

powered on and then changes to a high level after the high speed system oscillator is

stable. Therefore this flag will always be read as "1" by the application program after

device power-on. The flag will be low when in the SLEEP or IDLE0 Mode but after a

wake-up has occurred, the flag will change to a high level after

32

clock cycles if the

HIRC oscillator is used.

Bit 1

IDLEN:

IDLE Mode control

0: Disable

1: Enable

This is the IDLE Mode Control bit and determines what happens when the HALT

instruction is executed. If this bit is high, when a HALT instruction is executed the

device will enter the IDLE Mode. In the IDLE1 Mode the CPU will stop running

but the system clock will continue to keep the peripheral functions operational, if

FSYSON bit is high. If FSYSON bit is low, the CPU and the system clock will all stop

in IDLE0 mode. If the bit is low the device will enter the SLEEP Mode when a HALT

instruction is executed.

Bit 0

HLCLK:

system clock selection

0: f

H

/2 ~ f

H

/64 or f

L

1: f

H

This bit is used to select if the f

H

clock or the f

H

/2~f

H

/64 or f

L

clock is used as the

system clock. When the bit is high the f

H

clock will be selected and if low the

f

H

/2~f

H

/64 or f

L

clock will be selected. When system clock switches from the f

H

clock

to the f

L

clock and the f

H

clock will be automatically switched off to conserve power.