Rev. 1.10

54

November 26, 2019

Rev. 1.10

55

November 26, 2019

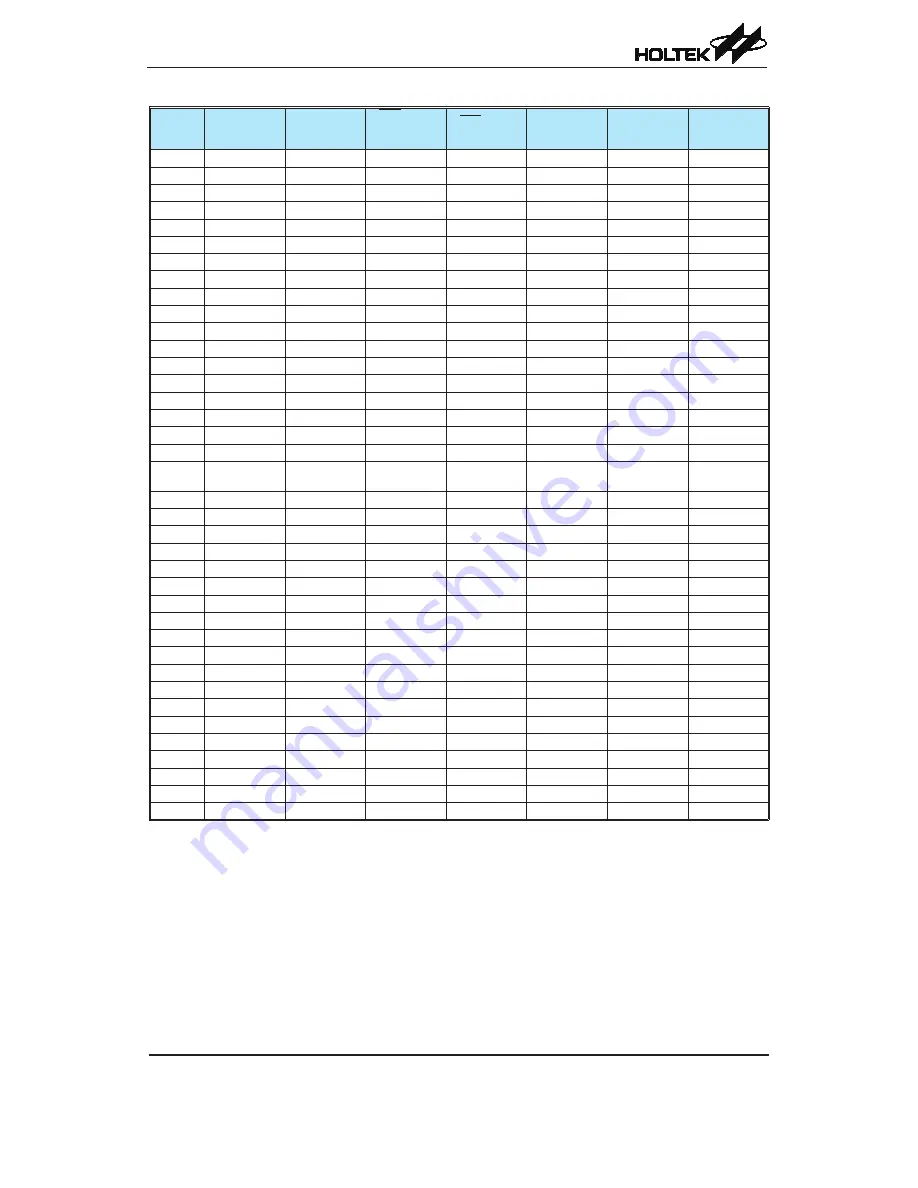

HT68FB240

USB Low Speed Flash MCU

Register

Reset

(Power On)

WDT Time-out

(Normal

Operation)

RES Reset

(Normal

Operation)

RES Reset

(HALT)

WDT Time-out

(HALT)*

USB-reset

(Normal)

USB-reset

(HALT)

TM1C0

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 u u u u u u u u 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

TM1C1

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 u u u u u u u u 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

TM1DL

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 u u u u u u u u 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

TM1DH

- - - - - - 0 0 - - - - - - 0 0 - - - - - - 0 0 - - - - - - 0 0 - - - - - - u u - - - - - - 0 0 - - - - - - 0 0

TM1AL

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 u u u u u u u u 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

TM1AH

- - - - - - 0 0 - - - - - - 0 0 - - - - - - 0 0 - - - - - - 0 0 - - - - - - u u - - - - - - 0 0 - - - - - - 0 0

FRCR

- - - 0 - - - 0 - - - 0 - - - 0 - - - 0 - - - 0 - - - 0 - - - 0 - - - u - - - u - - - 0 - - - 0 - - - 0 - - - 0

FCR

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 u u u u u u u u 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

FARL

x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x u u u u u u u u x x x x x x x x x x x x x x x x

FARH

- - - - x x x x - - - - x x x x - - - - x x x x - - - - x x x x - - - - u u u u - - - - x x x x - - - - x x x x

FD0L

x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x u u u u u u u u x x x x x x x x x x x x x x x x

FD0H

x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x u u u u u u u u x x x x x x x x x x x x x x x x

FD1L

x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x u u u u u u u u x x x x x x x x x x x x x x x x

FD1H

x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x u u u u u u u u x x x x x x x x x x x x x x x x

FD2L

x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x u u u u u u u u x x x x x x x x x x x x x x x x

FD2H

x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x u u u u u u u u x x x x x x x x x x x x x x x x

FD3L

x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x u u u u u u u u x x x x x x x x x x x x x x x x

FD3H

x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x u u u u u u u u x x x x x x x x x x x x x x x x

USB_

STAT

1 1 x x 0 0 0 - u u x x 0 0 u - u u x x 0 0 u - u u x x 0 0 u - u u x x 0 0 u - u u x x 0 0 u - u u x x 0 0 u -

UINT

- 0 0 0 - 0 0 0 - 0 0 0 - 0 0 0 - 0 0 0 - 0 0 0 - 0 0 0 - 0 0 0 - u u u - u u u - 0 0 0 - 0 0 0 - 0 0 0 - 0 0 0

USC

1 0 - 0 x 0 x x u u - u x u x x u u - u x u x x u u - u x u x x u u - u x u x x u u - u 0 1 0 0 u u - u 0 1 0 0

UCC

0 0 - 0 0 - x x u u - u u - x x u u - u u - x x u u - u u - x x u u - u u - u u u u - u u - 0 0 u u - u u - 0 0

AWR

x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

STL

- x x x - x x x - x x x - x x x - x x x - x x x - x x x - x x x - x x x - x x x - 0 0 0 - 0 0 0 - 0 0 0 - 0 0 0

SIES

x x - x x x x x x x - x x x x x x x - x x x x x x x - x x x x x x x - x x x x x 0 0 - 0 0 0 0 0 0 0 - 0 0 0 0 0

MISC

x x x - - x x x x x x - - x x x x x x - - x x x x x x - - x x x x x x - - x x x 0 0 0 - - 0 0 0 0 0 0 - - 0 0 0

UFEN

- 0 0 - - 0 0 0 - u u - - u u u - 0 0 - - 0 0 0 - 0 0 - - 0 0 0 - u u - - u u u - 0 0 - - 0 0 0 - 0 0 - - 0 0 0

FIFO0

x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x

FIFO1

x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x

FIFO2

x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x

URDCT

x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x u u u u u u u u 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

PWMC

0 - - - - 0 0 0 0 - - - - 0 0 0 0 - - - - 0 0 0 0 - - - - 0 0 0 u - - - - u u u 0 - - - - 0 0 0 0 - - - - 0 0 0

PWM0

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 u u u u u u u u 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

PWM1

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 u u u u u u u u 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

PWM2

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 u u u u u u u u 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

CTRL

0 - - - - x 0 0 0 - - - - x 0 0 0 - - - - x 0 0 0 - - - - x 0 0 u - - - - x u u 0 - - - - x 0 0 0 - - - - x 0 0

LVRC

0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 u u u u u u u u 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1

SYSC

1 - - - - - - - 1 - - - - - - - 1 - - - - - - - 1 - - - - - - - u - - - - - - - 1 - - - - - - - 1 - - - - - - -

Note: "u" stands for unchanged

"x" stands for unknown

"-" stands for unimplemented